Other Parts Discussed in Thread: UNIFLASH

Hello,

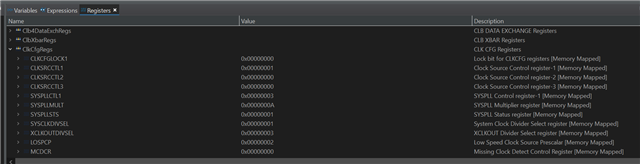

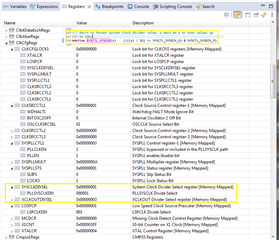

After weeks debugging code in CCS and later UniFlash I notice a pattern that seem to indicate PLL & dividers are running much faster after POR. Oddly this is not the case when HW Reset button is pushed several times after firmware load. The POR typically uses internal clock and switches to OSCLK in other MCU classes and has been troublesome in some devices. Symptoms (x49c) are flash API (OTP checksum cause NMI run from LSRAM), #pragma control data sections missing load data, bizarre application behavior all occur mostly after POR, not HW reset or SW reset. This PLL locking behavior is not detected when launching SDK's in CCS debug since XDC110 preempts the clocking to the target during firmware load as the OSCCLK is not clocking XTAL until run to main. This is a soft landing for the OSCCLK versus hard landing caused by POR event.

3.7.2.1 Oscillator Clock (OSCCLK)

One of INTOSC2, XTAL, or INTOSC1 must be chosen to be the master reference clock (OSCCLK) for the CPU and most of the peripherals. OSCCLK may be used directly or fed through the system PLL to reach a higher

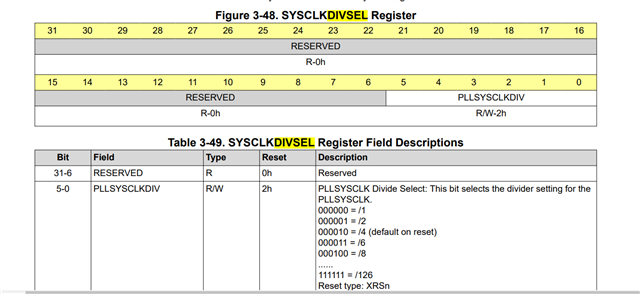

frequency. At reset, OSCCLK is the default system clock, and is connected to INTOSC2. Even when the SYSDIV 4 the PLL still seems to be running much faster after POR when the CPU should be clocking at 50MHz.

Has there been any extensive testing of PLL locking stability after POR? What can be done in the clock setting code to ensure the PLL locks after POR on all x49c MCU, not just a select few?

The clock setting code included in C200ware v4.01 was last update was 2021 though it looks like it could be root cause of many forum issues being reported.

MOSC_reset:

// Set up PLL control and clock dividers

// PLLSYSCLK = 20MHz (XTAL_OSC) * 10 (IMULT) * 1 (FMULT) / 2 (PLLCLK_BY_2)

CLK_Missing = SysCtl_setClock(SYSCTL_OSCSRC_XTAL |

SYSCTL_IMULT(10) |

SYSCTL_FMULT_NONE |

SYSCTL_SYSDIV(2) |

SYSCTL_PLL_ENABLE);

if(CLK_Missing == false)

{

SysCtl_resetMCD();

goto MOSC_reset;

}