Other Parts Discussed in Thread: TIDM-02010, SYSCONFIG

Hi,

Can you please help me in understanding how to configure the ADC module for a custom target board? I do not understand how the ADC is being configured in the following example:

// Three-shunt

#define MTR1_ADC_TRIGGER_SOC ADC_TRIGGER_EPWM1_SOCA // EPWM1_SOCA

#define MTR1_ADC_I_SAMPLEWINDOW 18

#define MTR1_ADC_V_SAMPLEWINDOW 26

#define MTR1_IU_ADC_BASE ADCC_BASE // ADCC-B12/C2*

#define MTR1_IV_ADC_BASE ADCB_BASE // ADCB-A11/B10*/C0

#define MTR1_IW_ADC_BASE ADCA_BASE // ADCA-A14*/B14/C4

#define MTR1_IU_ADCRES_BASE ADCCRESULT_BASE // ADCC-B12/C2*

#define MTR1_IV_ADCRES_BASE ADCBRESULT_BASE // ADCB-A11/B10*/C0

#define MTR1_IW_ADCRES_BASE ADCARESULT_BASE // ADCA-A14*/B14/C4

#define MTR1_IU_ADC_CH_NUM ADC_CH_ADCIN2 // ADCC-B12/C2*

#define MTR1_IV_ADC_CH_NUM ADC_CH_ADCIN10 // ADCB-A11/B10*/C0

#define MTR1_IW_ADC_CH_NUM ADC_CH_ADCIN14 // ADCA-A14*/B14/C4

#define MTR1_IU_ADC_SOC_NUM ADC_SOC_NUMBER1 // ADCC-B12/C2* -SOC1-PPB1

#define MTR1_IV_ADC_SOC_NUM ADC_SOC_NUMBER1 // ADCB-A11/B10*/C0 -SOC1-PPB1

#define MTR1_IW_ADC_SOC_NUM ADC_SOC_NUMBER1 // ADCA-A14*/B14/C4 -SOC1-PPB1

#define MTR1_IU_ADC_PPB_NUM ADC_PPB_NUMBER1 // ADCC-B12/C2* -SOC1-PPB1

#define MTR1_IV_ADC_PPB_NUM ADC_PPB_NUMBER1 // ADCB-A11/B10*/C0 -SOC1-PPB1

#define MTR1_IW_ADC_PPB_NUM ADC_PPB_NUMBER1 // ADCA-A14*/B14/C4 -SOC1-PPB1

Please let me know if you have any questions or would like additional information.

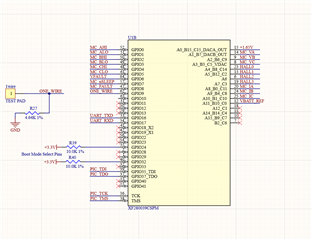

I can provide schematic reference for the setup of my target device with the F280039C if that helps.

Thank you,

William