Other Parts Discussed in Thread: C2000WARE

Hello,

My question is in two parts viz:

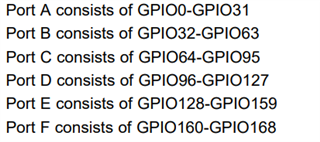

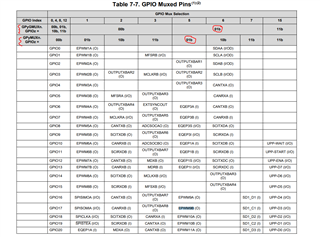

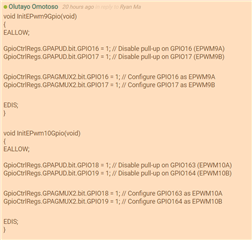

No. 1: I have 8 HR ePWM to control a converter. All of them have the same frequency and duty cycle but different phase shifts. I need one more PWM (call it ePWM 9A) to operate at 100% duty cycle. Can any of the normal PWMs 10 - 16 provide 100% duty cycle as pp 1786 of the Tech. Ref. Manual says that their is limitation to the duty cycle (12.5% - 87.5%)?

No. 2: If No. 1 is possible, how do I configure the ePWM9A to operate on 100% duty cycle having configured the first eight PWMs (HR ePWM) to operate at 50% duty cycle?

No. 3: I need to turn on ePWM 9A when certain condition is met. I am not savy in this regard (pardon me) but I'll explain this using the analogy below

if (A >B) {

Do not turn on ePWM 9A

All the 8 HR ePWM are swiching

}

else {

Turn on ePWM 9A;

All the 8 ePWM are still switching;

{

Therefore, how do I disable and enable ePWM 9A?

The below looks like a solution from previous answered questions:

"

Disable the PWM where x is the pwm No.

EALLOW;

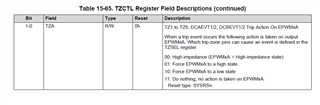

EpwmxRegs.TZFRC.bit.OST = 1;

EpwmxRegs.TZCTL.bit.TZA = 0x02; // fOR FORCE low

EpwmxRegs.TZCTL.bit.TZB = 0x02; //fOR fORCE loW

EDIS;

// Enable the PWM where x is the pwm No.

EALLOW;

EpwmxRegs.TZCTL.bit.OST = 0x01; // fOR FORCE low

EpwmxRegs.TZCTL.bit.OST = 0x01; //fOR fORCE loW

EDIS;

"

But the comment for both anable and disable pointed to force low. Please advise.

Regards,

Olutayo.