Hi Team,

There're some issues from the customer need your help:

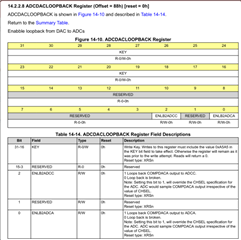

1. I don't see any diagram about DAC to ADC loopback in TRM and DS, so i wonder how it loopback?

2. There are four comparators in analog subsystem, each comparator have high and low two DACs. So there are eight DACs in total. In following picture COMPDACA refer to which DAC? And connect to which ADCA and ADCC channels?

Could you help check this case?

Thanks & Regards,

Ben