- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi champs,

I use CCS debug mode and run code standalone to study RESC register, it looks like the POR and XRSn bits of RESC register won't set to 1 when I reset F28388D device, is it reasonable?

In the TRM, there have no detailed bit filed description of NMISHDFLG register, where can I get the information for reference please?

Regards,

Luke

Hi Luke,

After a POR, the POR and XRSn register will be set to 1, and are then cleared by the boot ROM.

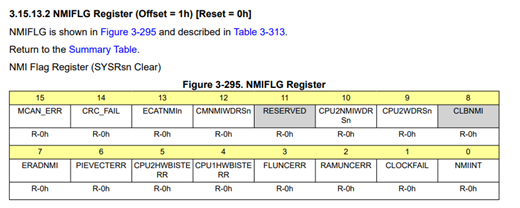

The detailed bit field description of the register(NMISHDFLG) can be found in the NMIFLG Register section.

Thanks

Aswin

Hi Aswin,

Boot code will clear POR and XRSn bits in RESC register, then when DSP re-boot due to unstable XRSn signal level, users have no chance to know this problem by checking RESC register.

May I know the background why boot code clear POR and XRSn bits?

Regards,

Luke

Hi Luke,

I am gathering information regarding this. Will get back to you shortly.

Thanks

Aswin

Hi Luke,

There is a section - Boot Status information in TRM, where you can find that the boot ROM stores the boot status information in a RAM location so that user can read the boot status and take necessary action.

The CPU boot ROM health and booting status is written to a 32 bit address in M0RAM.

The CPU1 Boot Status Bit Fields table describes the different status during booting.

Thanks

Aswin