Hi champs,

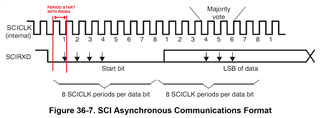

In below picture, we show the SCI communication format. My customer has two questions,

- What's the delay time before SCI starts sampling?

- Does SCI module samples signal at SCKCLK rising edge?

Please advise your comments, thanks for help.

Thanks and regards,

Luke