Part Number: TMS320F280049

Other Parts Discussed in Thread: SN65HVD230

Hi Experts,

Seeking your assistance please:

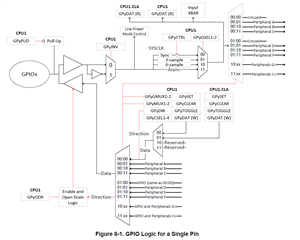

We observe an error on the CAN Bus after starting the µC, there is an dominate bit of 120ms my first question is: are there different pullup resistors in the µC depending of the selected mode? example pin initialized as GPIO the pullup is different to pin initialized as CAN TX/RX?

One more thing, With the first prototype we had no problems, µC and SN65HVD230 are connected directly.

At the seconde prototype we had to add a galvanically isolation, see picture. now it looks, that the internal pullup of the µC can be different as mentioned before In seems that the CAN TX is high but the ADUM1201 brings the voltage down, but after setting the bit rate of the internal controller the pin is stable high.

Regards,

Archie A.