Hi Expert,

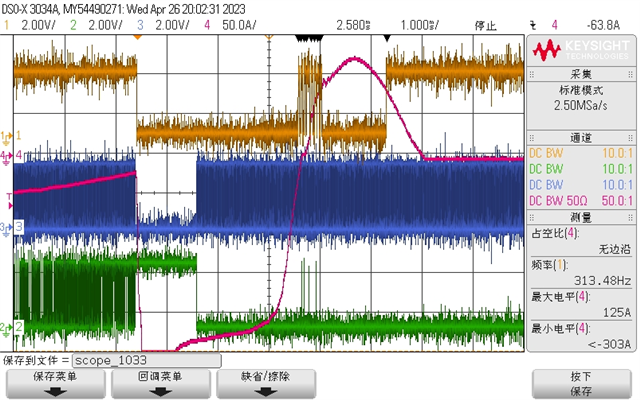

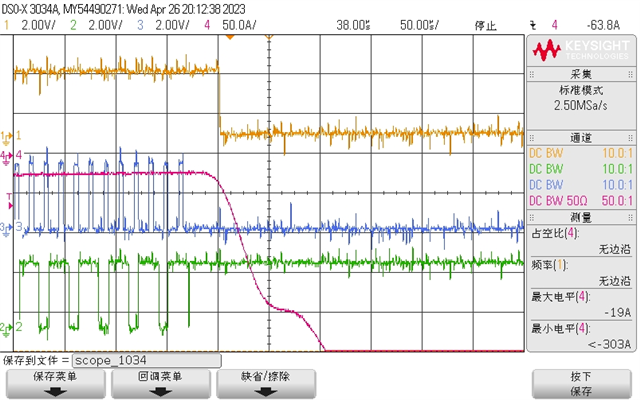

My customer are using F280034 for power switching control, seem there have some noise that lead to MCU failure, which will generate about 260us long high level pulse, then burn the IGBT module.

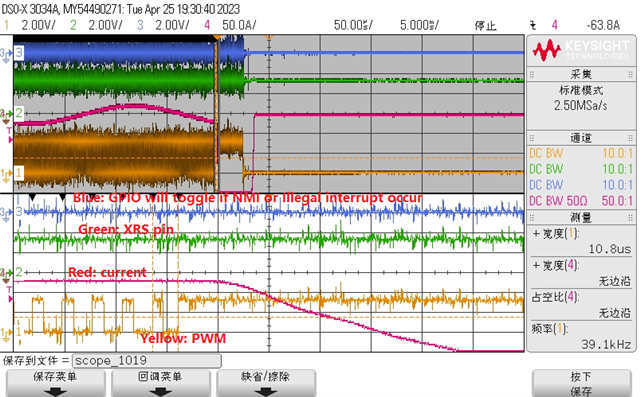

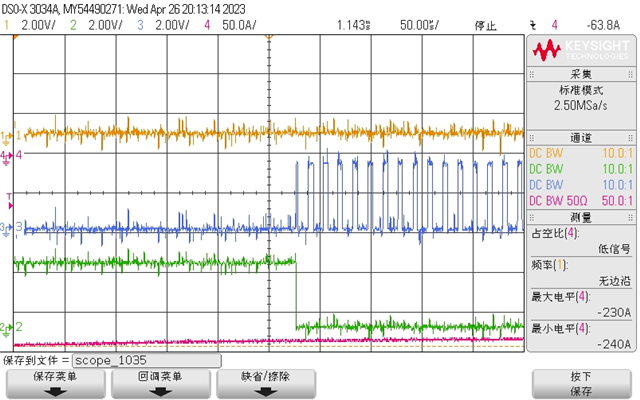

They capture the waveform as below, Red one is current waveform, yellow is EPWM2B from MCU which will have a very long high level pulse, then lead to over current.

blue is gpio toggle signal at PWM interrupt, also is abnormal to when issue occur.

Customer have configure TZ1 for over current protection, they have verified TZ1 can signal well by suddenly add a very big load and TZ1 can be trigger to shun down PWM.

but in this case when there have some noise( connected to probe of scope will increase noise), TZ1 does not work to go to protection.

Emulator can not be connected to see the status of MCU as this is test in aging oven.

but from waveform that seem MCU still working and may have missing clock without reset.

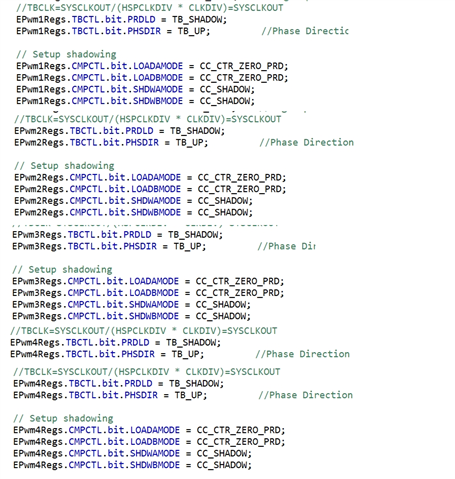

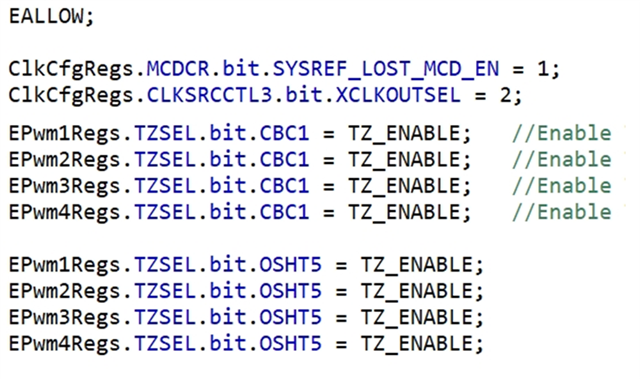

I suggest them to add TZ5 configure for clock fail, they use OSC2 for clock, configure as below:

But seem does not work and TZ5 seem not happen to shut down PWM, any missing to configure TZ5? any other suggestion to help fix this issue? thanks.