Other Parts Discussed in Thread: SYSCONFIG

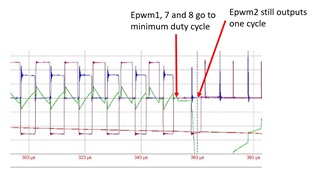

unexpected pulse at epwm2.

The configuration that we have done is:

Epwm1 is the master of epwm2, 7 and 8

All work with phase 0

Their periods are all sync with TBPRDLINK.

GLDMODE is done when the counter reaches Z(0).

All are configured in one shot mode OSHTMODE=1

We change the pwm CMPA and CMPB registers dynamically from a CLA task synchronized with the period of the pwm

we have observed that occasionally, when changing from a certain on time (something like 40% duty cycle) to a very low value (t1_cnts and t2_cnts lower than the deadtime), epwm2 takes one extra cycle to output that value, while all other modules do it immediately.