Hi to all,

do you have any update for me?

Thanks a lot

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Nicola

I have to say sorry. I could not get a chance to go through the code u shared with me.

One thing you can check for is MIPS overflow. What is the frequency of the ISR where you are using SPLL? Can you set a gpio at the beginning of the ISR and reset just before the end of the ISR, can check pulse width of the GPIO. It should be less than ISR period.

Thanks

Amir

Dear Amir,

thank a lot for your reply. I understand that you are very busy so don't worry.

I followed your advice, using GPIOs for debugging is something I always do.

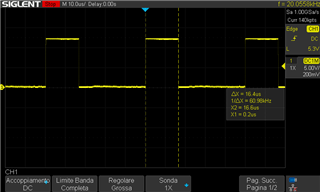

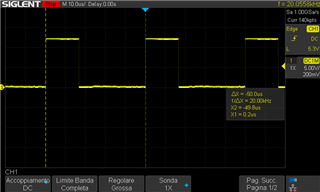

I have an interrupt every 50us (20Khz timer ISR like writed in the Solar library), and the width of the interrupt is 16.4us.

See attached pictures for your reference.

Looking forward to receive your feedback,

Thank you and Best regards

Hi Nicola

So its not ISR overflow. Can you try disabling certain part of codes in steps? This may give an idea what part of code in causing the issue.

Thanks

Amir

Dear Amir,

as I told you in the previous mails, I tried to remove a lot of firmware parts but the result is the same.

I have only some (positive) changes when I remove or swap some variables declarations.

When you have the time you can try with the code that I sent you.

Best regards

Nicola

Hello Nicola

Sure. I will try to do that. Given the current work load, it may take time (may be 2 months) to start working on that.

Thanks

Amir