Part Number: TMS320F28379D

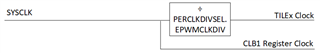

From E2E design support forums, I get the information that the highest frequency of CLB is 100 MHz and it is clocked to the EPWM with a divider.

From:e2e.ti.com/.../launchxl-f28379d-launchxl-f28379d-clb-clock-frequency

Based on this information I have following questions

1. The EPWM highest working frequency is 200MHz. EPWM module has lot of outputs to CLB. This outputs are signal with highest frequency of 200MHz. So how can I config the CLB to guarantee the CLB module(100MHz) can process the input signal from EPWM? Or if the signal timing width is smaller than CLB timing period, CLB cannot deal with this situation?

2. Also from Table26-2 I find CLB has local input from ECAP/CPU outputs which working frequency may be 200MHz? How can I config the CLB for these input signal?