Hi Team, seeking some support for a customer

Facing a problem due to the appearance of interrupt overflows of ADC.

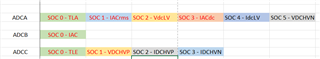

I have 11 measurements to acquire : i put 6 measure on ADCA, 1 on ADCB, and 4 on ADCC.

I use only one interrupt, linked to EOC5 on ADCA as it shall be the last one to be acquired.

Every SOC is triggered by EPWM1, with a frequency of 200kHz.

On the interrupt of ADCA1, I store the value in a table of 32 values.

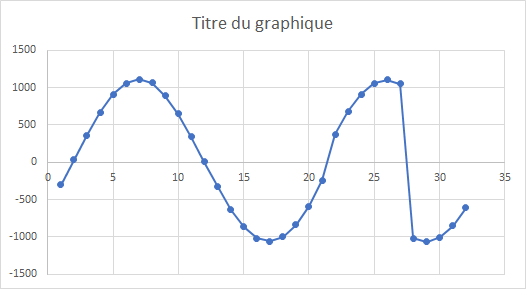

In input on the board, I have a perfect sinus voltage. However, in my table, I usually get parts of it :

The value in my table can be (for example) :

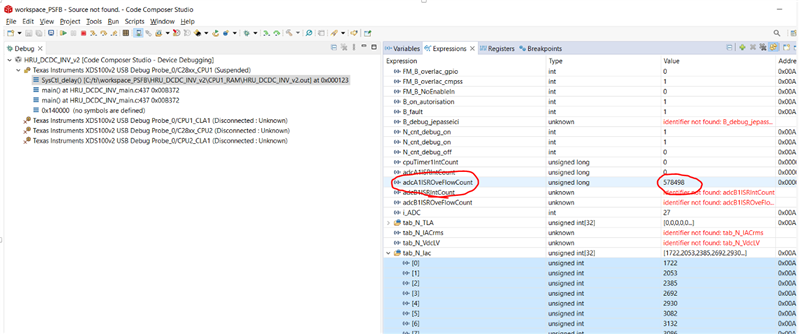

I checked the interrupt overflow counter and it increases all the time.

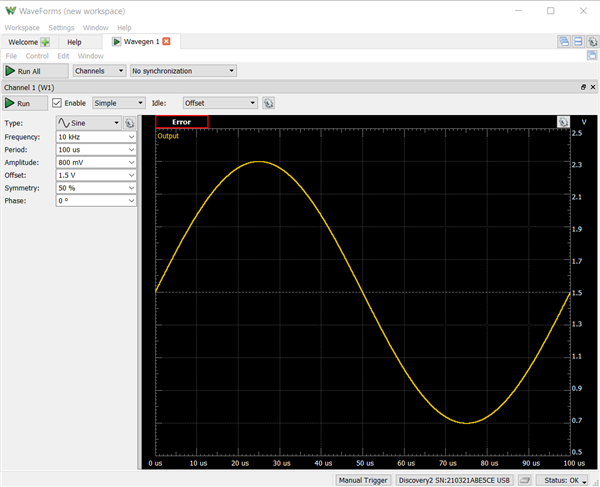

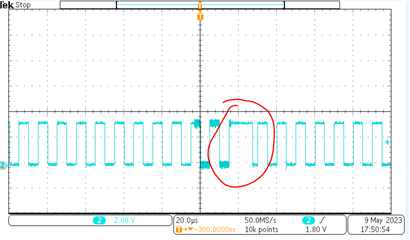

To investigate a bit more, each time the ADCA1 interrupt is called, i toggle a gpio output : I should see a perfect sware wave signal at a frequency of 100Khz but that it is not the case :

It confirms there are overflows.

As the ADC is capable of 3.3MSps in 12 bits, a frequency of 200kHz should not be a problem, even with 6 channels used on ADCA.

Do you have an idea what is wrong in my understanding ?

____________________-

Thank you very much in advance.

-Mark