Part Number: TMS320F28379D

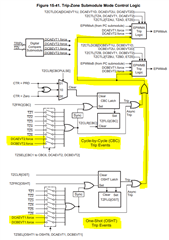

I am trying to add CBC that handles both positive and negative high current on a 4 switch buck/boost converter. I have the CMPSS HI and LOW to handle the polarity of the current so that is not not a problem. The problem I am trying to figure out is how to setup different actions on the PWM A and B outputs depending on whether in BUCK or BOOST mode and still maintain the actions setup for the Oneshot trips. I understand that I may have to change action settings while running. If that is possible. I have the following questions.

- I noticed there are priorities for the actions

Output EPWMxA:

– TZA (highest) -> DCAEVT1 -> DCAEVT2 (lowest)

– TZAU (highest) -> DCAEVT1U -> DCAEVT2U (lowest)

– TZAD (highest) -> DCAEVT1D -> DCAEVT2D (lowest)

Output EPWMxB:

– TZB (highest) -> DCBEVT1 -> DCBEVT2 (lowest)

– TZBU (highest) -> DCBEVT1U -> DCBEVT2U (lowest)

– TZBD (highest) -> DCBEVT1D -> DCBEVT2D (lowest)

Does the "do nothing" setting automatically give the next "non do nothing" setting priority? For example If TZA is set to 3 or do nothing and DCAEVT1 is set to 2 or FORCE LOW. If a DCAEVT1 trips does it force PWMA low or does it do nothing? Or if I set TZA to FORCE LOW and DCAEVT1 to FORCE HI and a DCAEVT1 comes in will PWMA be FORCE HIGH or LOW? - If I change from buck mode to boost mode which will require different actions can I reload the action registers safely without issues