Part Number: TMS320F28386D

Other Parts Discussed in Thread: SYSCONFIG, C2000WARE,

Hi Experts

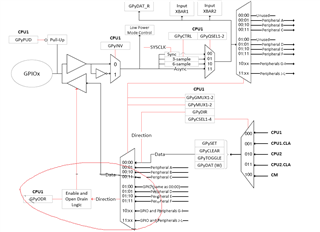

I wanted to use CLB block to control the motor commutation taking the 3 hall inputs and few more inputs to Generate 6 outputs.

For that I am thinking to use 3 LUTs and 3 OUTLUTs from each tile(2 tiles)

Please help me how to map GPIO inputs to the CLB and how to take outputs of the CLB to GPIOs

Thanks & Regards

K.Aravind