Part Number: TMS320F28032

Hi Experts,

I am asking for my customer here.

Customer are encountering the AQCSFRC cannot pull EPWMxA low.

They use S/W to write "0x1" to AQCSFRC.CSFA on EPWM1, EPWM2, EPWM3, and find that only EPWM2 cannot pull EPWM2A low, other EPWM1A, EPWM3A are right. EPWM2A would be always high, But after about 200ms, EPWM2A can become low level by AQCSFRC.CSFA. Due to the fault was discovered by the end customer, it is impossible to locate the issue through hardware method.

So, we check the below step:

#1.F2803x ADC sampling and communication can work normally, system clock is normal.

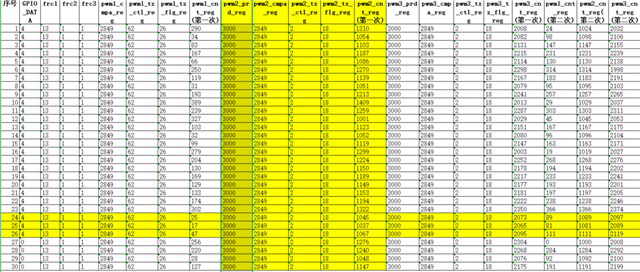

#2.We use 20ms interrupt to read the register value of EPWM. Like EPWM1.TBPRD, EPWM2.TBPRD, EPWM3.TBPRD both right 3000, AQCSFRC both "0x01", EPWM2.TZFLG = 18; EPWM2.TZCTL = 2, GPIO_DATA about the PWM output pin, PWM1A is 0; PWM2A is 1; PWM3A is 0. So, PWM2A is not normally pulled low.

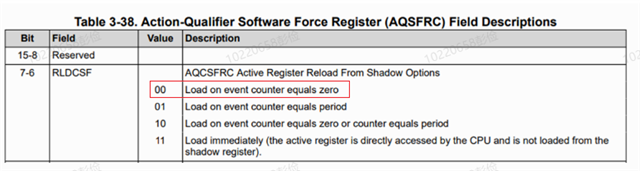

#3.We check the loadmode about AQCSFRC, load on event counter equals zero. We would check the Zero Event whether to generate.

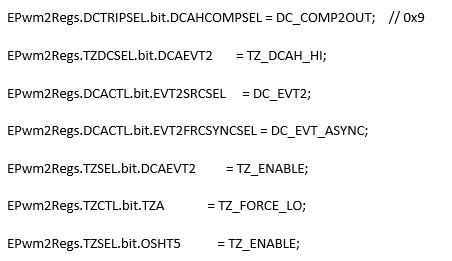

#4.We check the TZ configuration code, found that EPWM2 CBC and DCAEVT2 generate.

#5.it will be phase shifted between PWM1A, PWM2A, PWM3A. PWM1A is master, and Phase Shift 120° to PWM2A, Phase Shift 240° to PWM3A.

Is it the phase shift that is causing the zero crossing event to be lost for a long time? Are there other reasons? Any suggestions for other software exclusions? Thanks a lot~