Hello,

I've noticed that PWM register writes in the CLA take significantly more time than the same writes by the CPU. For CLA writes I am seeing roughly 8-9 clock cycles per write and for the CPU I see about 2 clock cycles per write.

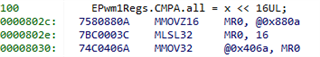

I'm able to see this difference with the line below copied into either my CLA code or my CPU main ISR. However, I see the same difference if the "100.0" is a float variable, so I don't think it is a compiler optimization effect

EPwm1Regs.CMPA.bit.CMPA = 100.0;

I am timing the instruction in the CPU by breakpointing on the instruction, resetting the Profile Clock in code composer and then stepping through the instruction.

I am timing the instructions in the CLA using a PWM counter (PWM8) setup in the below code and then I subtract the counter value before/after the instruction

timer_count1 = EPwm8Regs.TBCTR;

EPwm1Regs.CMPA.bit.CMPA = 100;

timer_count2 = EPwm8Regs.TBCTR-timer_count1;

I got the overhead of the timer access and subtraction by just doing the above timer code without anything in the middle as per below

timer_count1 = EPwm8Regs.TBCTR;

timer_count2 = EPwm8Regs.TBCTR-timer_count1;

The final clock counts were

CPU Instruction: 2

CLA Timer Overhead: 8

CLA Timer Minus Overhead: 16 - 8 = 8

Is this differential expected or does something seem to be off?

Thanks,

Jason

EALLOW;

EPwm8Regs.TBPRD = 32000; // Set period for ePWMx

EPwm8Regs.TBCTR = 0x0000; // Clear counter

EPwm8Regs.TBCTL.bit.CLKDIV = TB_DIV1; // Time-base Clock Prescale Bits

EPwm8Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // High-Speed Time-base Clock Prescale Bits

EPwm8Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; // EPWMx is a "slave", sync flow-through

//EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE; // EPWMx is a "slave", Load the time-deg counter from TBPHS at sync

EPwm8Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Up-Down Count Mode

EDIS;