Part Number: TMS320F28388D

Other Parts Discussed in Thread: C2000WARE

We have a sporadic problem that should be solved seriously.

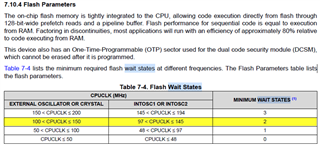

The software runs in flash from the CM of the TMS320F28388D ( FRDCNTL.RWAIT=2, CPUCLK = 120MHz).

Sometimes an NMI interrupt is triggered and the CM jumps to the interrupt routine "nmiISR1" where I have set a breakpoint.

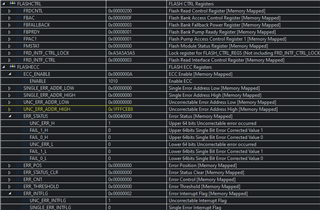

The registers then always show the following picture:

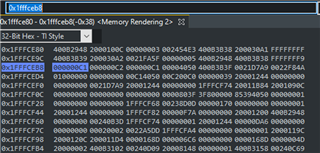

So the cause of the interrupt is an uncorrectable error at address 0x1FFFCEB8. This is always the same address. But this address points to the C1 RAM, which has no ECC. It points to the local variable "i" in the stack. This value is not the same for every attempt.

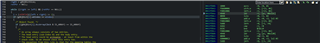

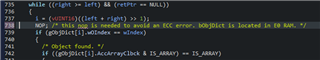

When jumping back into the code after the interrupt routine, it is always at the same place:

Here wIndex is compared with the object table and this is in the E0 RAM, which has an ECC. So the error does not happen randomly, but always at this place.

If a NOP is inserted here, the error no longer occurs. Also if FRDCNTL.RWAIT=4 is set, the error does not occur any more.

According to the specification FRDCNTL.RWAIT=2 should be sufficient for a CPUCLK of 120 MHz.

The solution with the NOP is more efficient than setting RWAIT=4, since two additional CLK cycles are not waited for each flash access.

The same problem I can see on a second target.

But does this solution cover the whole problem? What is actually the cause for this behavior?

Best regards

Simon