Other Parts Discussed in Thread: C2000WARE, REF3430, OPA320

Dear expert,

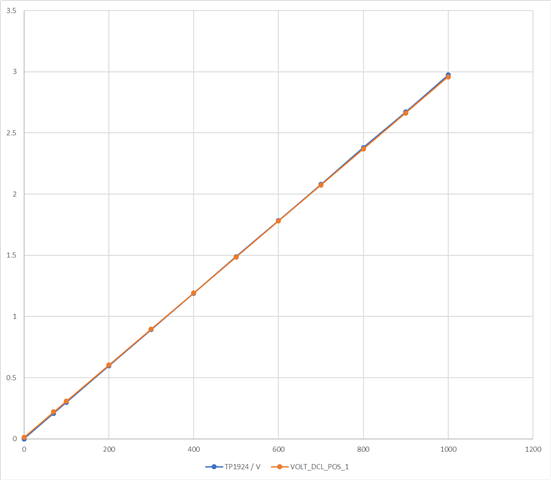

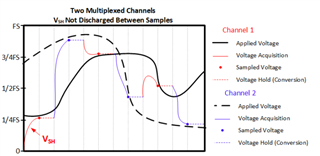

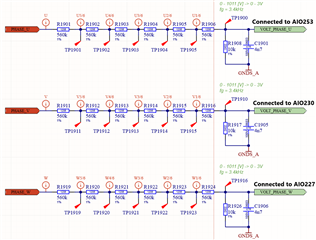

We are currently developing our application for TMS320F280039, and find out one of the ADC measurements is slightly higher from the expected value (AIO229), and it looks like pin is internally pulled-up. When we measure at the microcontroller pin.

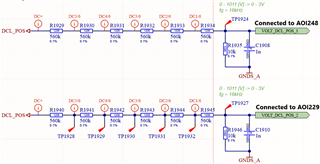

To debug are comparing two pins ( AIO229 and AIO248) which, after reviewing, apparently have the same configuration(no pull up, no inversion, sync), but AIO229 shows this "offset".

Also, when measuring with a tester AIO229, the value is higher than expected, and after disconnecting AIO229 from the circuit, the measured value goes back to the "expected" voltage.

Do you know if there is any HW difference between these two pins that could provoke this? Or else, can you foresee any specific configuration that could lead to this behavior?

Regards,

Marc Ferrer

Ra = 300e, Rb = 1k, R1957 = 121k

Ra = 300e, Rb = 1k, R1957 = 121k