Hi Expert,

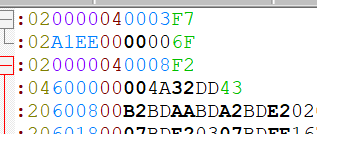

My customer are using F28388D, there have data for the RAM address 0x0003A1EE when generate hex file,

FLASH12 : origin = 0x0BC000, length = 0x002000 /* on-chip Flash */

FLASH13 : origin = 0x0BE000, length = 0x001FF0 /* on-chip Flash */

// FLASH13_RSVD : origin = 0x0BFFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000800

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000800

anything wrong here?