Other Parts Discussed in Thread: C2000WARE

Hi,

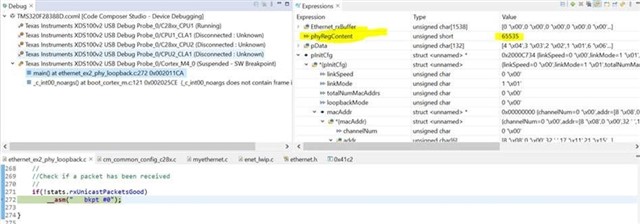

customer uses the DP83825 instead of the DP83822 on their HW now. The C2000ware Eth examples didn't work anymore. I read that only the ID's (PHYIDR2, reg 0x3) are different. In which file do I have to change it? Are there any other things my customer has to change?

Regards, Holger