Part Number: TMS320F28386S

Hi team,

I have questions about EOS flag use-case, I am referring TRM now.

On "20.7 EOS and Interrupt Operation" mentions aout EOS pulse and register flag to use for interrupt event.

Q1. Is EOC flag set up on "20.15.2.4 ADCINTFLG Register"?

Q2. Under the settings below, we want to use EOC timing but not use interrupt. Is EOC flag set up on it even EOC interrupt is not used?

AdcaRegs.ADCCTL1.bit.INTPULSEPOS = 1; // ADC interrupt position. Set at the las of conversion

AdcaRegs.ADCINTSEL1N2.bit. INT1E=0; // disable interrupt

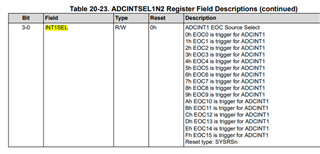

AdcaRegs.ADCINTSEL1N2.bit. INT1SEL=5; // EOC source of ADCINT1 is EOC5

Q3. If Q2 answer is "Yes" which means the flag is set up, When is the flag up? after the SOC0 or after the SOC5?

Sorry for the ambiguous questions but we do not have EVM in my hand and I am not familiar with this kind of questions.

Please tell me if you have any questions.

Best regards,

Yuto