Part Number: TMS320F28379D

Other Parts Discussed in Thread: TMS320F28379S, C2000WARE

Hello,

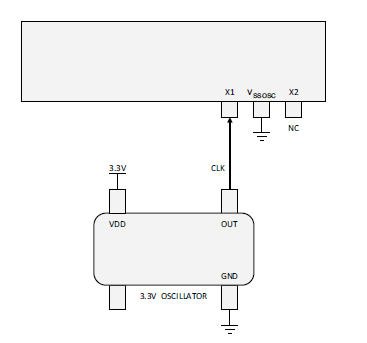

I have a custom board, and I'm using the TMS320F28379D. When I program into flash, it works fine. However, when I power cycle the board, it seems to get stuck waiting for the CLk (an external, single ended 20MHz oscillator). If I reprogram with CCS, it again works fine but get's stuck on power cycle.

Issues:

- MCU get's stuck on power cycle.

- I have another board with the TMS320F28379S and it doesn't have this issue.

- If I heat up the MCU with a reflow station, it doesn't exhibit this issue. As it's cooling down, it takes longer and longer to boot from power cycle. (3s, 7s, 20s, ..., never boots up).

Any suggestions how to further debug this or what could be the issue? I've validated the following:

- External CLK

- MCU VDD, VDDIO, etc.

- reset pin

- Boot mode pins (GPIO72 and GPIO84) are both pulled HIGH

Thanks so much.