Other Parts Discussed in Thread: C2000WARE, CONTROLSUITE

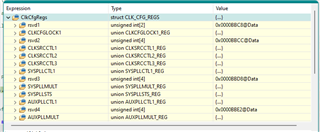

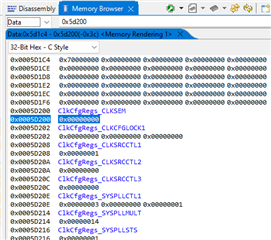

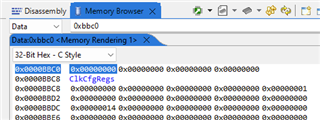

I am encountering an issue when trying to build for an F28377S device my company has manufactured. The computer where firmware development has been occurring has not had any issues running their builds. However, when we tried setting up development on a new machine (mine), the program/application locks up inside InitSysPll. The function is called as InitSysPll(XTAL_OSC,IMULT_20,FMULT_0,PLLCLK_BY_2); as normal. However, when the multiplier is written, the PLL never locks. It gets stuck in this while loop:

while(ClkCfgRegs.SYSPLLSTS.bit.LOCKS != 1)

{

//

// Uncomment to service the watchdog

//

// ServiceDog();

}

How can I fix this?

For information, I am using CCS 12 and debugging with an XDS100v2 JTAG probe.