Hello Everyone,

I am trying to configure EPWM module for TMDSCNCD28P65X control card, but having some issue in EPWM synchronisation. I have called configured EPWM 1 and EPWM 2 as follows for

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

EPwm1_Init();

EPwm2_Init();

EPwm3_Init();

EPwm5_Init();

EPwm18_Init();

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

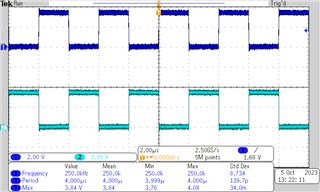

However, there is some phase delay of approximately 20n sec between the two module. Please note I have enable phase register for both EPWM 1 and EMPW 2 and set it to zero. In order to circumvent this problem I have configured EMPW 18 to act as a clk source for EPWM 1 and EMPM 2, in this case both the 1&2 are synced. I want to understand why TBCLKSYNC is not synchronizing the EPWM module.