Hello,

I have an application which initializes the ADC A and B and maps some channels to corresponding SOCs. As I am new to this DSP, I needed some clarity on the same.

1. Physically or in hardware, are there 4 ADC modules namely A,B,C,D each having 16 channels? (as per the technical reference manual, there are 4 I have noticed. Wanted to verify if there are 4 different hardware circuits or some form of muxing is present in between them to share the same 16 channels.)

2. If there are multiple ADC modules, do each of these modules have 16 SOCs or there are only 16 SOC circuitry being shared by all 4 modules? The Adc a,b,c,d registers are having different base addresses, I understand.

3. I have initialised the SOCFRC bit and set it to 1 for all SOCs in my initialization of ADCs file. I am a bit confused regarding how will it be cleared. The reason being, I am using ADCINT1 for triggering my conversion start. But the first start of conversion needs to be started by software forcing and once it starts as and when my conversion gets completed, the ADCINT1 will be triggered and again the conversion will start from SOC0. So the need for SOCFRC to be set 1 is one time. I am not clearing the SOCFRC bit anywhere in my code, so is it cleared by hardware somehow after one time use?

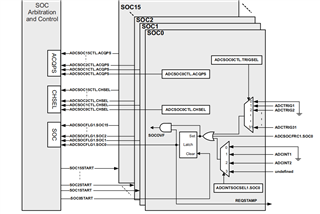

In the diagram shown, there are 3 sources of triggering the SOC, the SOCFRC, the ADCINT and some PWM triggers. My doubt is if SOCFRC is not cleared after the first time, then we donot need to wait for ADCINT to start the 2nd cycle of conversion again (which is desirable in my case as I need to start the 2nd cycle of conversion only after all the SOCs in my 1st cycle has been completed). As it is an OR gate before so any bit in the input, if high, will trigger an output high and hence SOC will begin. So the SOCFRC must be cleared somehow, so as to ensure that my ADCINT1 only triggers the 2nd cycle of SOC. \

It will be very helpful if you could clarify the above issues.

Thanks and Regards,

Prarambhik