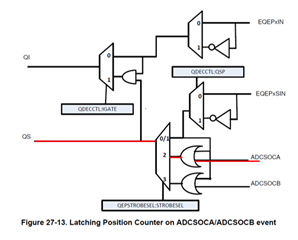

I'm attempting to trigger the latching of the position counter's value with the ADCSOCA, but the value of QPOSSLAT remains at 0 without updating.

Is there any part of the configuration that is incorrect, or are there any other registers that should be checked?