Other Parts Discussed in Thread: TMDSCNCD280039C, TMDSHSECDOCK

Dear Texas Instruments Team,

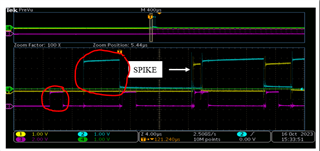

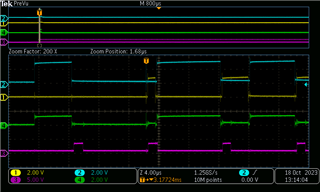

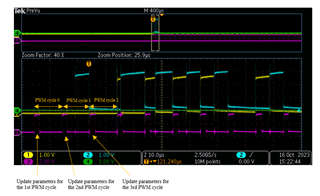

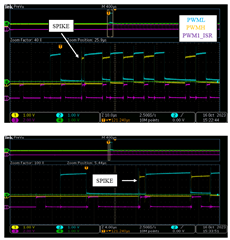

At the moment, I am developing the software to control the LLC converter. As you already know during the startup asymmetrical PWM is required for a first few PWM cycles, and later the symmetrical complementary PWM mode is needed. In the attached Figure, first 6 PWM cycles shows an example for PWM pattern during the startup procedure for LLC.

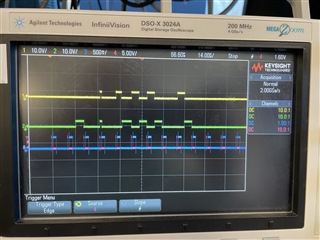

Figure 1: PWM pattern for startup procedure.

Here are some notes for first six PWM patterns:

1st PWM cycle – only low side MOSFET shall be turned on. High side MOSFET is turned off. PWM is not working in complementary mode.

2nd PWM cycle – both, low side and high side MOSFETs shall be turned off. PWM is not working in complementary mode.

3rd PWM cycle – low side and high side MOSFET operate at complementary mode where duty cycle for high-side MOSFET is smaller compared to the low side MOSFET.

4th PWM cycle - low side and high side MOSFET operate at complementary mode where duty cycle for high-side MOSFET is smaller compared to the low side MOSFET, but the ration between low side and high side duty cycle is now changed. Duty cycle for high side MOSFET is increased and duty cycle for low side is decreased.

5th PWM cycle - low side and high side MOSFET operate at complementary mode with the symmetrical PWM pattern – duty cycle for both PWM signals is 50 %.

6th PWM cycle - low side and high side MOSFET operate at complementary mode with the symmetrical PWM pattern – duty cycle for both PWM signals is 50 %.

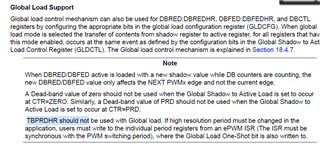

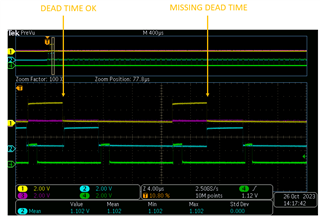

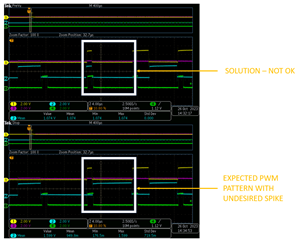

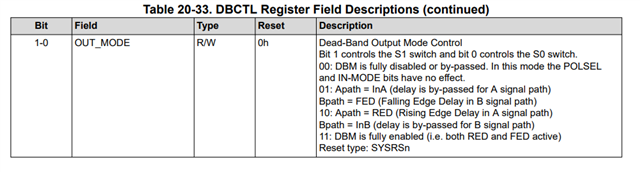

I attached the main.c file used to test the startup PWM pattern. Inside the PWM interrupt, the PWM parameters are updated for every new PWM cycle. To make everything transparent and synchronous, the global load option is selected to update all the required registers at the same time. The problem which occurs is with the start of 3rd PWM cycle where smaller spike occurs at the start of the PWM cycle. This is not spike caused by the interference or neither it is introduced by the bad measurement setup. My assumption is that it happens because the Dead Band Submodule is bypassed in 2nd PWM cycle and in the 3rd PWM cycle is enabled. But I do not understand why because the global load is enabled. Can you please tell me why is this happening and how to solve an issue with the spike. This behaviour is not acceptable.

/******************************************************************************/

/* COPYRIGHT (c) 2023 */

/* AEconversion */

/* All rights reserved. */

/******************************************************************************/

/*!

* @file main.c

* @author Haris Kovacevic

* @date September 19, 2023

* @brief Main function

* @version V1.0.0

*/

/******************************************************************************/

/*!

* @addtogroup MAIN

* @{ <!-- BEGIN GROUP -->

*/

/******************************************************************************/

/******************************************************************************/

/* Includes */

/******************************************************************************/

#include "device.h"

#include "interrupt.h"

#include "sw_interrupt_prioritization_logic.h"

/******************************************************************************/

/* Definitions */

/******************************************************************************/

/******************************************************************************/

/* Typedefs */

/******************************************************************************/

/******************************************************************************/

/* Variables */

/******************************************************************************/

extern uint16_t RamfuncsLoadStart;

extern uint16_t RamfuncsLoadEnd;

extern uint16_t RamfuncsLoadSize;

extern uint16_t RamfuncsRunStart;

extern uint16_t RamfuncsRunEnd;

extern uint16_t RamfuncsRunSize;

extern uint16_t Cla1ProgLoadStart;

extern uint16_t Cla1ProgRunStart;

extern uint16_t Cla1ProgLoadSize;

volatile uint32_t cnt_test = 0UL;

/******************************************************************************/

/* Function prototypes */

/******************************************************************************/

__interrupt void pwm1_isr (void);

static void flash_init (void);

static void cpu_init (void);

static void gpio_init (void);

static void pwm_init (void);

/******************************************************************************/

/* Functions */

/******************************************************************************/

/******************************************************************************/

/*

* MAIN FUNCTION

*/

/******************************************************************************/

void main(void)

{

/* Copy time critical code and flash setup code to RAM.

* The RamfuncsLoadStart, RamfuncsLoadSize, RamfuncsRunStart, Cla1ProgRunStart,

* Cla1ProgLoadStart, and Cla1ProgLoadSize are created by the linker.

* Refer to the device .cmd file. */

memcpy((uint32_t *)&RamfuncsRunStart, (uint32_t *)&RamfuncsLoadStart,

(uint32_t)&RamfuncsLoadSize );

memcpy((uint32_t *)&Cla1ProgRunStart, (uint32_t *)&Cla1ProgLoadStart,

(uint32_t)&Cla1ProgLoadSize );

/* Initialize PIE and clear PIE registers. Disables CPU interrupts. */

Interrupt_initModule();

/* Initialize the PIE vector table with pointers to the shell Interrupt

Service Routines (ISR). */

Interrupt_initVectorTable();

/* Flash initialization */

flash_init();

/* CPU initialization */

cpu_init();

/* GPIO initialization */

gpio_init();

/* PWM initialization */

pwm_init();

/* Enable PWM 1 interrupt */

Interrupt_enable(INT_EPWM1);

/* Enable sync and clock to PWM */

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

/* Enable Global Interrupt (INTM) and realtime interrupt (DBGM) */

EINT;

ERTM;

while(1)

{

/* Infinite loop */

}

}

/******************************************************************************/

/*

* FLASH INITIALIZATION

*/

/******************************************************************************/

static void flash_init(void)

{

/* Set the bank fallback power modes to active */

Flash_setBankPowerMode(FLASH0CTRL_BASE, FLASH_BANK0, FLASH_BANK_PWR_ACTIVE);

Flash_setBankPowerMode(FLASH0CTRL_BASE, FLASH_BANK1, FLASH_BANK_PWR_ACTIVE);

Flash_setBankPowerMode(FLASH0CTRL_BASE, FLASH_BANK2, FLASH_BANK_PWR_ACTIVE);

/* Power up flash bank and pump and this also sets the fall back mode of

* flash and pump as active */

Flash_setPumpPowerMode(FLASH0CTRL_BASE, FLASH_PUMP_PWR_ACTIVE);

/* Disable cache and prefetch mechanism before changing wait states */

Flash_disableCache(FLASH0CTRL_BASE);

Flash_disablePrefetch(FLASH0CTRL_BASE);

/* Set waitstates according to frequency */

Flash_setWaitstates(FLASH0CTRL_BASE, 5);

/* Enable cache and prefetch mechanism to improve performance of code

* executed from flash */

Flash_enableCache(FLASH0CTRL_BASE);

Flash_enablePrefetch(FLASH0CTRL_BASE);

/* At reset, ECC is enabled. If it is disabled by application software and

* if application again wants to enable ECC. */

Flash_enableECC(FLASH0ECC_BASE);

/* Force a pipeline flush to ensure that the write to the last register

* configured occurs before returning */

__asm(" RPT #7 || NOP");

}

/******************************************************************************/

/*

* CPU INITIALIZATION

*/

/******************************************************************************/

static void cpu_init(void)

{

/* Disable Watchdog */

SysCtl_disableWatchdog();

SysCtl_setClock(SYSCTL_OSCSRC_OSC1 |

SYSCTL_IMULT(24U) |

SYSCTL_REFDIV(2U) |

SYSCTL_ODIV(1U) |

SYSCTL_SYSDIV(1U) |

SYSCTL_PLL_ENABLE);

/* Set Low speed clock divider */

SysCtl_setLowSpeedClock(SYSCTL_LSPCLK_PRESCALE_4);

/* Clock source connected to output pin */

SysCtl_selectClockOutSource(SYSCTL_CLOCKOUT_SYSCLK);

SysCtl_setXClk(SYSCTL_XCLKOUT_DIV_1);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_TIMER0);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_TIMER1);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_TIMER2);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM1);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM2);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM3);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM4);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM5);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM6);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM7);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM8);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_HRCAL);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_SCIA);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_SCIB);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_ADCA);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_ADCB);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_ADCC);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CMPSS1);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CMPSS2);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CMPSS3);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CMPSS4);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_DACA);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_DACB);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CLB1);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CLB2);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CLB3);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CLB4);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CLA1);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_ECAP1);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_ECAP2);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_ECAP3);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_I2CA);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_I2CB);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_SPIA);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_SPIB);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CANA);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_MCANA);

}

/******************************************************************************/

/*

* GPIO INITIALIZATION

*/

/******************************************************************************/

static void gpio_init(void)

{

/* Configure GPIO pin 0 */

GPIO_setDirectionMode(0, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(0, GPIO_PIN_TYPE_STD);

GPIO_setMasterCore(0, GPIO_CORE_CPU1);

GPIO_writePin(0, (uint32_t)0);

GPIO_setPinConfig(GPIO_0_EPWM1_A);

/* Configure GPIO pin 1 */

GPIO_setDirectionMode(1, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(1, GPIO_PIN_TYPE_STD);

GPIO_setMasterCore(1, GPIO_CORE_CPU1);

GPIO_writePin(1, (uint32_t)0);

GPIO_setPinConfig(GPIO_1_EPWM1_B);

/* Configure GPIO pin 44 */

GPIO_setDirectionMode(44, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(44, GPIO_PIN_TYPE_STD);

GPIO_setMasterCore(44, GPIO_CORE_CPU1);

GPIO_writePin(44, (uint32_t)0);

GPIO_setPinConfig(GPIO_44_GPIO44);

}

/******************************************************************************/

/*

* PWM INITIALIZATION

*/

/******************************************************************************/

static void pwm_init(void)

{

/* Disable sync (Freeze clock to PWM as well) */

SysCtl_disablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

/* Connect interrupt functions to vector addresses */

Interrupt_register(INT_EPWM1, &pwm1_isr);

/* Set PWM counter type and clock dividers */

EPWM_setTimeBaseCounterMode(EPWM1_BASE, EPWM_COUNTER_MODE_UP);

EPWM_setTimeBaseCounter(EPWM1_BASE, 0U);

EPWM_setClockPrescaler(EPWM1_BASE, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1);

EPWM_setTimeBasePeriod(EPWM1_BASE, 1200U);

/* Set PWM emulation mode */

EPWM_setEmulationMode(EPWM1_BASE, EPWM_EMULATION_FREE_RUN);

/* Phase shift load setup */

EPWM_disablePhaseShiftLoad(EPWM1_BASE);

EPWM_setPhaseShift(EPWM1_BASE, 0U);

/* Set PWM period load configuration */

EPWM_setPeriodLoadMode(EPWM1_BASE, EPWM_PERIOD_SHADOW_LOAD);

EPWM_selectPeriodLoadEvent(EPWM1_BASE, EPWM_SHADOW_LOAD_MODE_COUNTER_ZERO);

/* Set PWM compare register load configuration and initial duty cycle */

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE, EPWM_COUNTER_COMPARE_A, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE, EPWM_COUNTER_COMPARE_B, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE, EPWM_COUNTER_COMPARE_C, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(EPWM1_BASE, EPWM_COUNTER_COMPARE_D, EPWM_COMP_LOAD_ON_CNTR_ZERO);

/* Action qualifier setting */

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(EPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierT1TriggerSource(EPWM1_BASE, EPWM_AQ_TRIGGER_EVENT_TRIG_TZ_1);

EPWM_setActionQualifierT2TriggerSource(EPWM1_BASE, EPWM_AQ_TRIGGER_EVENT_TRIG_TZ_1);

/* Set Dead-Band settings for Complementary Mode */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = 0x4U; // All writes and reads to bits [5:0] of the DBCTL register are shadowed

EPWM_setDeadBandCounterClock(EPWM1_BASE, EPWM_DB_COUNTER_CLOCK_FULL_CYCLE);

EPWM_setRisingEdgeDeadBandDelayInput(EPWM1_BASE, EPWM_DB_INPUT_EPWMA);

EPWM_setRisingEdgeDelayCount(EPWM1_BASE, 25U);

EPWM_setDeadBandDelayPolarity(EPWM1_BASE, EPWM_DB_FED, EPWM_DB_POLARITY_ACTIVE_LOW);

EPWM_setFallingEdgeDeadBandDelayInput(EPWM1_BASE, EPWM_DB_INPUT_EPWMA);

EPWM_setFallingEdgeDelayCount(EPWM1_BASE, 25U);

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x5; // Force PWM1 A and B to LOW state

/* Set compare values */

EPWM_setCounterCompareValue(EPWM1_BASE, EPWM_COUNTER_COMPARE_A, 0U);

EPWM_setCounterCompareValue(EPWM1_BASE, EPWM_COUNTER_COMPARE_B, 6000U);

/* Enable PWM1 interrupt */

EPWM_setInterruptSource(EPWM1_BASE, EPWM_INT_TBCTR_ZERO);

EPWM_enableInterrupt(EPWM1_BASE);

EPWM_setInterruptEventCount(EPWM1_BASE, 1U);

/* Global load configuration */

EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_TBPRD_TBPRDHR);

EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_CMPA_CMPAHR);

EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_CMPB_CMPBHR);

//EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_CMPC);

//EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_CMPD);

EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_DBRED_DBREDHR);

EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_DBFED_DBFEDHR);

EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_DBCTL);

EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_AQCTLA_AQCTLA2);

EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_AQCTLB_AQCTLB2);

EPWM_enableGlobalLoadRegisters(EPWM1_BASE, EPWM_GL_REGISTER_AQCSFRC);

EPWM_setGlobalLoadEventPrescale(EPWM1_BASE, 1U);

EPWM_disableGlobalLoadOneShotMode(EPWM1_BASE);

EPWM_setGlobalLoadTrigger(EPWM1_BASE, /*EPWM_GL_LOAD_PULSE_CNTR_PERIOD*/EPWM_GL_LOAD_PULSE_CNTR_ZERO);

EPWM_enableGlobalLoad(EPWM1_BASE);

//EPWM_disableGlobalLoad(EPWM1_BASE);

}

/******************************************************************************/

/*

* PWM1 ISR

*/

/******************************************************************************/

__interrupt void pwm1_isr(void)

{

HWREG(GPIODATA_BASE + GPIO_O_GPBSET) = (0x1U << 12U);

/* Save IER register on stack */

volatile uint16_t tempPIEIER = HWREGH(PIECTRL_BASE + PIE_O_IER3);

/* Set the global and group priority to allow CPU interrupts

with higher priority */

IER |= M_INT3;

IER &= MINT3;

HWREGH(PIECTRL_BASE + PIE_O_IER3) &= MG3_1;

/* Enable Interrupts */

Interrupt_clearACKGroup(0xFFFFU);

__asm(" NOP");

EINT;

/* Code to execute inside interrupt */

switch(cnt_test)

{

case 0:

/******************************** 1st PWM CYCLE ********************************/

#if 0

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

/* Force PWM1 A and PWM1 B is defined by CMPA register and counter equal to

* period/zero */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x1;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0/*0xC0*/;

#endif

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 0UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_AQCTLA) = 0x0012U;

HWREGH(EPWM1_BASE + EPWM_O_AQCTLB) = 0x0201U;

/* Force PWM1 A and PWM1 B is defined by CMPA register and counter equal to

* period/zero */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x0;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0/*0xC0*/;

/* All writes and reads to bits[5:0] of the DBCTL registers are shadowed. */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = 0x4U;

/* Bypass dead band submodule */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL) = 0x0C08U;

cnt_test += 1U;

/*******************************************************************************/

break;

case 1:

/******************************** 2nd PWM CYCLE ********************************/

#if 0

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0;

/* Force PWM1 A and B to LOW state */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x5;

#endif

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 0UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 0UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_AQCTLA) = 0x0012U;

HWREGH(EPWM1_BASE + EPWM_O_AQCTLB) = 0x0102U;

/* Force PWM1 A and PWM1 B is defined by CMPA register and counter equal to

* period/zero */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x0;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0/*0xC0*/;

/* All writes and reads to bits[5:0] of the DBCTL registers are shadowed. */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = 0x4U;

/* Bypass dead band submodule */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL) = 0x0C08U;

cnt_test += 1U;

/*******************************************************************************/

break;

case 2:

/******************************** 3rd PWM CYCLE ********************************/

#if 0

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 150UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 150UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0;

/* Forcing for PWM1 A and B is disabled */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x0;

#endif

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 150UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 150UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_AQCTLA) = 0x0012U;

HWREGH(EPWM1_BASE + EPWM_O_AQCTLB) = 0x0102U;

/* All writes and reads to bits[5:0] of the DBCTL registers are shadowed. */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = /*0x4U*/0x4U;

/* Bypass dead band submodule */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL) = 0x0C0B/*0x0C0A*//*0x0C09*/;

cnt_test += 1U;

/*******************************************************************************/

break;

case 3:

/******************************** 4th PWM CYCLE ********************************/

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 450UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 450UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0;

/* Forcing for PWM1 A and B is disabled */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x0;

/* All writes and reads to bits[5:0] of the DBCTL registers are shadowed. */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = /*0x4U*/0x4U;

/* Bypass dead band submodule */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL) = 0x0C0B;

cnt_test += 1U;

/*******************************************************************************/

break;

case 4:

/******************************** 5th PWM CYCLE ********************************/

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0;

/* Forcing for PWM1 A and B is disabled */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x0;

/* All writes and reads to bits[5:0] of the DBCTL registers are shadowed. */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = /*0x4U*/0x4U;

/* Bypass dead band submodule */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL) = 0x0C0B;

cnt_test += 1U;

/*******************************************************************************/

break;

case 5:

/******************************** 6th PWM CYCLE ********************************/

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

/* All writes and reads to bits[5:0] of the DBCTL registers are shadowed. */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = 0x4U;

/* Bypass dead band submodule */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL) = 0x0C0B;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0;

/* Force PWM1 A and B to LOW state */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x0;

cnt_test += 1U;

/*******************************************************************************/

break;

case 6:

/******************************** 7th PWM CYCLE ********************************/

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0;

/* Force PWM1 A and B to LOW state */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x5;

/* All writes and reads to bits[5:0] of the DBCTL registers are shadowed. */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = 0x4U;

/* Bypass dead band submodule */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL) = 0x0C08/*0x0C0A*/;

cnt_test += 1U;

/*******************************************************************************/

break;

case 7:

/******************************** 8th PWM CYCLE ********************************/

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0;

/* Force PWM1 A and B to LOW state */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x0;

/* All writes and reads to bits[5:0] of the DBCTL registers are shadowed. */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = 0x4U;

/* Bypass dead band submodule */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL) = /*0x0C0B*/0x0C09;

cnt_test += 1U;

/*******************************************************************************/

break;

case 8:

/******************************** 9th PWM CYCLE ********************************/

/* Update PWM parameters */

HWREGH(EPWM1_BASE + EPWM_O_TBPRD) = 1200UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPA + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_CMPB + 0U + 0x1U) = 600UL;

HWREGH(EPWM1_BASE + EPWM_O_DBRED) = 25UL;

HWREGH(EPWM1_BASE + EPWM_O_DBFED) = 25UL;

/* Load on time-base counter equals zero */

HWREGH(EPWM1_BASE + EPWM_O_AQSFRC) = 0x0;

/* Force PWM1 A and B to LOW state */

HWREGH(EPWM1_BASE + EPWM_O_AQCSFRC) = 0x5;

/* All writes and reads to bits[5:0] of the DBCTL registers are shadowed. */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL2) = 0x4U;

/* Bypass dead band submodule */

HWREGH(EPWM1_BASE + EPWM_O_DBCTL) = 0x0C08;

cnt_test += 1U;

/*******************************************************************************/

break;

default:

break;

}

/* Clear interrupt flag */

EPWM_clearEventTriggerInterruptFlag(EPWM1_BASE);

/* Acknowledge this interrupt to receive more interrupts from group 3 */

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP3);

/* Disable interrupts and restore registers saved */

DINT;

HWREGH(PIECTRL_BASE + PIE_O_IER3) = tempPIEIER;

HWREG(GPIODATA_BASE + GPIO_O_GPBCLEAR) = (0x1U << 12U);

}