Part Number: TMS320F28386D

Other Parts Discussed in Thread: C2000WARE

Hello,

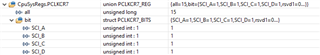

I've been working with a TI DSP and am having issues configuring the SCI Peripheral.

The issue that I'm seeing is that the registers that I'm writing to are not actually changing.

I checked that the SCI B peripheral's clock is enabled.

Any assistance would be greatly appreciated. Code Below:

Thank You,

Dan Brescia

void init_SCI(void)

{

ScibRegs.SCICTL1.bit.SWRESET = holdReset;

//Communication Control Register

ScibRegs.SCICCR.bit.STOPBITS = oneStopBit;

ScibRegs.SCICCR.bit.PARITY = evenParity; //Doesn't matter because it's disabled

ScibRegs.SCICCR.bit.PARITYENA = disableParity;

ScibRegs.SCICCR.bit.LOOPBKENA = disableLoopBack;

ScibRegs.SCICCR.bit.ADDRIDLE_MODE = pointToPointMode;

ScibRegs.SCICCR.bit.SCICHAR = eightBitsPerChar;

//Control Register 1

ScibRegs.SCICTL1.bit.RXERRINTENA = disabledRxErrorInterrupt;

ScibRegs.SCICTL1.bit.TXWAKE = txSleep; //--DB Understand this bit better

ScibRegs.SCICTL1.bit.SLEEP = rxWake;

ScibRegs.SCICTL1.bit.TXENA = txDisable;

ScibRegs.SCICTL1.bit.RXENA = rxEnable;

//Baud Rate

int x = ( (calculateBaudRateClockDivider(desiredBaudRate, lowSpeedPeripheralClockRate) ) & 0xFF00) >> 8;

ScibRegs.SCIHBAUD.bit.BAUD = x;

int y = (calculateBaudRateClockDivider(desiredBaudRate, lowSpeedPeripheralClockRate) ) & 0x00FF;

ScibRegs.SCILBAUD.bit.BAUD = y;

//Control Register 2

ScibRegs.SCICTL2.bit.RXBKINTENA = rxDisableInterrupt;

ScibRegs.SCICTL2.bit.TXINTENA = txDisableInterrupt;

//Tx FIFO Register

ScibRegs.SCIFFTX.bit.SCIRST = sciFIFOReset;

ScibRegs.SCIFFTX.bit.SCIFFENA = sciFIFODisable;

ScibRegs.SCIFFTX.bit.TXFIFORESET = txFIFOReset;

ScibRegs.SCIFFTX.bit.TXFFIENA = txFIFOInterruptDisabled;

//Rx FIFO Register

ScibRegs.SCIFFRX.bit.RXFIFORESET = rxFIFORESET;

ScibRegs.SCIFFRX.bit.RXFFIENA = rxFIFOInterruptDisabled;

//Auto-Baud Detection Register

ScibRegs.SCIFFCT.bit.CDC = autoBaudDetectAlignmentDisabled;

//Debug Behaviour Register

ScibRegs.SCIPRI.bit.FREESOFT = stopOnSuspend;

ScibRegs.SCICTL1.bit.SWRESET = releaseReset;

return;

}

#include "f2838x_device.h" #ifndef NAI_VPX_SCI_H_ #define NAI_VPX_SCI_H_ //SCI Communication Control Register (SCICCR) Macros #define oneStopBit (0x00) #define evenParity (0x00) #define disableParity (0x00) #define disableLoopBack (0x00) #define pointToPointMode (0x00) #define eightBitsPerChar (0x07) //SCI Control Register 1 (SCICTL1) Macros #define disabledRxErrorInterrupt (0x00) #define releaseReset (0x01) #define holdReset (0x00) #define txSleep (0x00) #define txWake (0x01) #define rxWake (0x01) #define txEnable (0x01) #define txDisable (0x00) #define rxEnable (0x01) #define rxDisable (0x00) //Baud Rate Calculation & Constants #define lowSpeedPeripheralClockRate (50000000) //50MHz #define desiredBaudRate (115200) //115.2kHz #define calculateBaudRateClockDivider(desiredBaud,LSPCLK) (((LSPCLK) / (8 * (desiredBaud))) - 1) //SCI Control Register 1 (SCICTL1) Macros #define rxDisableInterrupt (0x00) #define txDisableInterrupt (0x00) //SCI Tx FIFO Register (SCIFFTX) Macros #define sciFIFOReset (0x00) #define sciFIFODisable (0x00) #define txFIFOReset (0x00) #define txFIFOInterruptDisabled (0x00) //SCI Rx FIFO Register (SCIFFRX) Macros #define rxFIFORESET (0x00) #define rxFIFOInterruptDisabled (0x00) //Auto-Baud Detection Register #define autoBaudDetectAlignmentDisabled (0x00) //Debug Behaviour Register #define stopOnSuspend (0x00) //Function Prototypes void init_SCI(void); void SCI_Machine(void);