Part Number: TMS320F2800157

Other Parts Discussed in Thread: C2000WARE

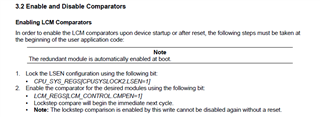

From TRM of LCM section.

I feel that I don not get enough information to use it. Do you have more detailed document for lockstep function?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS320F2800157

Other Parts Discussed in Thread: C2000WARE

From TRM of LCM section.

I feel that I don not get enough information to use it. Do you have more detailed document for lockstep function?

1. The note under figure 3-1 in your TRM, it said the primary/secondary module of can be either a CPU or a peripheral, so where can I set the primary/secondary module of LCM?

2. Section3.1.1 said LCM has pipelined architecture. Is LCM pipeline architecture correspond with the pipeline architecture of the CPU?

From SPRU430F, I know TI CPU has eight pipeline stage. For example, If there is different in the 3rd stage between primary/secondary CPU, will LCM detect these different immediately in its corresponding architecture? Or the LCM just monitor the IO of the CPU(such as databus?) and the different in the 3rd stage between primary/secondary CPU will be detected by LCM only when IO of CPU is different?

3. In section 7.11 of databook, it said C2000 Safety Package for Automotive and Industrial Real-Time Microcontrollers User's Guide has some more information of LCM self test. But I don't know which article should I refer in these user guide.

1. The note under figure 3-1 in your TRM, it said the primary/secondary module of can be either a CPU or a peripheral, so where can I set the primary/secondary module of LCM?

Is LCM pipeline architecture correspond with the pipeline architecture of the CPU?

Yes, this is just another redundant core to verify the first core's output is correct.

If there is different in the 3rd stage between primary/secondary CPU, will LCM detect these different immediately in its corresponding architecture?

The LCM is only meant to compare the output of the core, not the individual pipeline stages in between.

C2000 Safety Package for Automotive and Industrial Real-Time Microcontrollers User's Guide has some more information of LCM self test. But I don't know which article should I refer in these user guide.

The two highlighted items below show the available safety collateral for F280015x

Regards,

Vince

Hi Liu,

There is no DMA on F280015x, it is mentioned as a general statement for all devices with LCM, where the DMA may have a redundant module too (no devices exist with this at this time). The only LCM option that is available on F280015x is the CPU.

Regards,

Vince

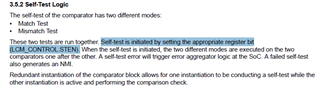

From TRM section 3.5.1 I know redundant comparator block and it enables availability of one comparator block during self-test of the other comparator block.

I want further know that will the redundant comparator undergo self-test when LCM_CONTROL.STEN = 1?

Or the redundant comparator is just to monitor the CPU when comparator1 in self-test?

Or the redundant comparator is just to monitor the CPU when comparator1 in self-test?

Please read the Match Test Mode and Mismatch Test Mode sections of the TRM. These directly explain how each redundant comparator is used during the test.

Please read the Match Test Mode and Mismatch Test Mode sections of the TRM. These directly explain how each redundant comparator is used during the test.

So can I thinks that LCM only use comparator1 in function mode?

For the comparator2, It is used to monitor the primary/secondary CPU during comparator1 is in self test. when comparator1 complete the self-test, the comparator2 begin self-test and comparator1 is used to monitor the primary/secondary CPU.

So can I thinks that LCM only use comparator1 in function mode?

For the comparator2, It is used to monitor the primary/secondary CPU during comparator1 is in self test. when comparator1 complete the self-test, the comparator2 begin self-test and comparator1 is used to monitor the primary/secondary CPU.

This is correct.