Part Number: LAUNCHXL-F28379D

Other Parts Discussed in Thread: C2000WARE

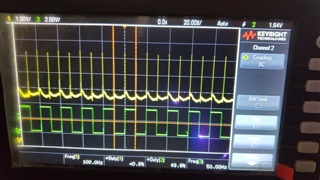

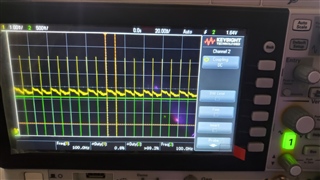

Hi, I'm trying to establish a SPI communication between two 28379D Launchpads. I have configured one as a Master and one as slave. When I execute both of them, I see that the received data in the Master launchpad is very random, it sometimes shows the value from the slave, sometimes directly the sent data on the MOSI line. I'm trying to use the CPU timers for executing the SPI write and read as I need them to be executed at a specific time interval. I have attached the code I have for SPI master setup and the write and read commands in the cputimer interrupt. How do I resolve this issue?

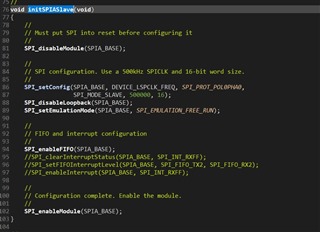

void initSPIBMaster(void)

{

//

// Must put SPI into reset before configuring it

//

SPI_disableModule(SPIB_BASE);

//

// SPI configuration. Use a 500kHz SPICLK and 16-bit word size.

//

SPI_setConfig(SPIB_BASE, DEVICE_LSPCLK_FREQ, SPI_PROT_POL0PHA0,

SPI_MODE_MASTER, 500000, 16);

SPI_disableLoopback(SPIB_BASE);

SPI_setEmulationMode(SPIB_BASE, SPI_EMULATION_FREE_RUN);

//

// FIFO and interrupt configuration

//

SPI_disableFIFO(SPIB_BASE);

//SPI_clearInterruptStatus(SPIB_BASE, SPI_INT_TXFF);

//SPI_setFIFOInterruptLevel(SPIB_BASE, SPI_FIFO_TX2, SPI_FIFO_RX2);

//SPI_enableInterrupt(SPIB_BASE, SPI_INT_TXFF);

//

// Configuration complete. Enable the module.

//

SPI_enableModule(SPIB_BASE);

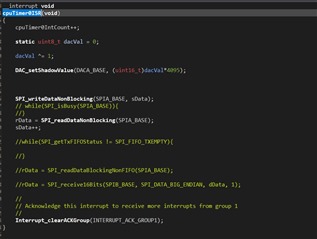

}__interrupt void

cpuTimer0ISR(void)

{

cpuTimer0IntCount++;

static uint8_t dacVal = 0;

dacVal ^= 1;

DAC_setShadowValue(DACA_BASE, (uint16_t)dacVal*4095);

SPI_writeDataBlockingFIFO(SPIB_BASE, sData);

while(SPI_isBusy(SPIB_BASE)){

}

rData = SPI_readDataNonBlocking(SPIB_BASE);

//

// Acknowledge this interrupt to receive more interrupts from group 1

//

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP1);

}

Also, if I need to just receive data from slave as SPI Master, which function do I need to use. I'm using device drivers library provided by TI.

We are trying to setup a BMS Master using this launch pad, so would need to be able to send a register address and then receive information of number of cell voltages and temperatures. Suggest steps that would take us close to achieve this.

Thank you in advance for any response and feel free to revert with any questions for more information.