Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

Hello,

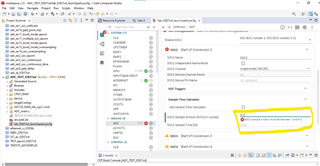

In my application EPWM switching frequency = 50khz & ADC clock frequency is 50 MHZ, SYS clock = 200MHZ. once EPWM triggers the ADC, i want to sample each SOCS with sampling frequency of 250kHz (i..e sampling time is 4000ns). when i started configuring the SYSConfig tool it is taking sampling time max upto 2560ns. Is there any way to increase the sampling time using SYSCONFIG tool?

please refer the attachment. Any way to configure the ADCSOC's with required sample time?