Other Parts Discussed in Thread: UCC21520, AMC1301

Hi,Team

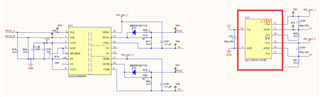

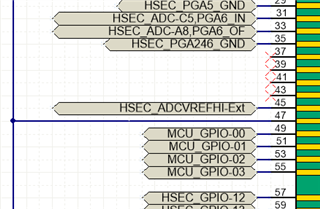

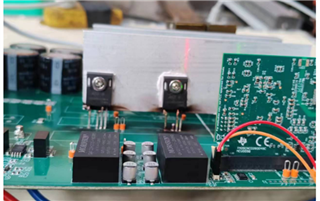

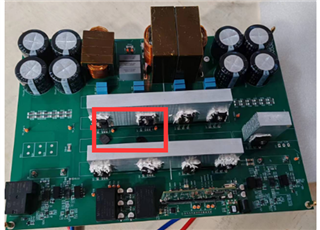

I designed a LLC prototype with an input of 800V and an output of 200V-750V, with a power of 20kW. The rated output voltage is 650V, and the resonant frequency is 150kHz. The switching frequency ranges from 100kHz to 400kHz, and if it exceeds 400kHz, it is changed to PWM control. At the beginning, 80V input is used, and the output can be adjusted from 20V to 75V, which can achieve hybrid control of PFM and PWM. However, the temperature of the switch tube in the red box in the figure below is relatively high, while the temperature rise of the switch tube in the blue box is almost negligible. Using a fan to blow can control the temperature rise of the red part, and then I conduct a high voltage experiment.

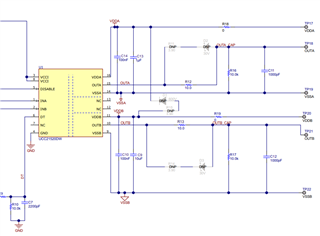

Fig.1

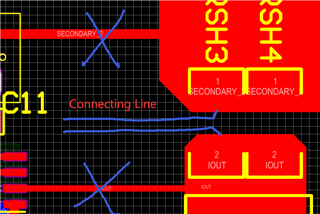

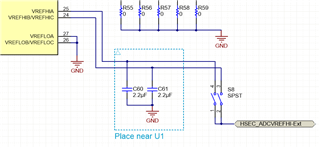

When the input voltage rose to 200V, the red part of the SiC MOSFETs was broken. In Figure 1, two SiC MOSFETs with a rated voltage of 1200V and a rated current of 30A were connected in parallel. During the experiment, the power was relatively small, and only one was connected. In Figure 2, the metal pins SiC MOSFETs source pole were all blown out.

Fig.2

I analyzed the reason and it seems that there is a problem with the buffer circuit. This buffer circuit was used to buffer the switching transistor when I designed PFC before. So I dismantled all the buffer capacitors and redo the experiment with low voltage 80V input. The red part of the SiC MOSFETs in Figure 1 generates heat just like the blue one, without blowing a fan, it didn't generate heat.. Then I raised voltage to 100V for the experiment, and the output of 80V was OK. When I raised voltage to 200V , there was no problem with the output of 80V. The second time the voltage was raised to 200V,SiC MOSFETs damaged again when outputting 160V. This time, the red part in Figure 1 was broken, and a piece of the black part collapsed, as shown in Figure 3

Fig.3

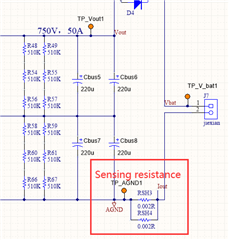

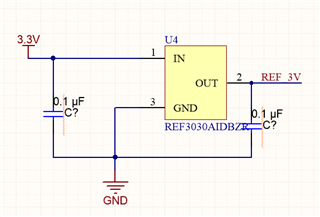

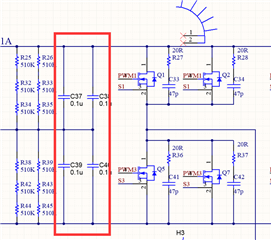

Is it possible that the voltage rise of the 0.1U filtering capacitor in Figure 4 is too fast, or is the voltage rise rate too fast?

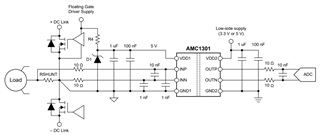

Fig.4

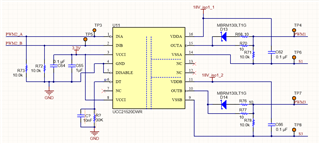

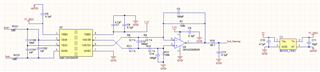

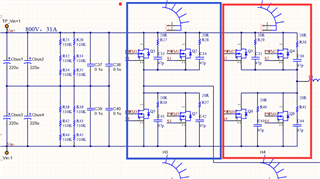

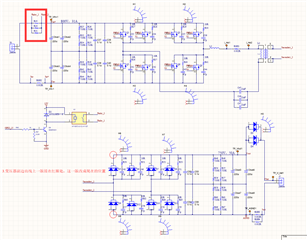

I use UCC21520 as the driver chip for SiC MOS, with a driving voltage of 20V and a dead band of 200ns.

Fig.5

During the experiment, the resistance in the red frame in Figure 5 was not connected and was short circuited. So I'm worried that the voltage rise rate is too fast.