Hi, experts,

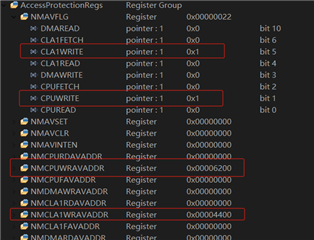

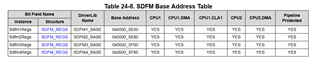

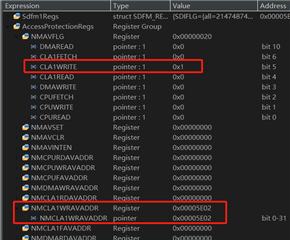

I got a problem while testing the sdfm routine "sdfm_ex2_filter_sync_claread". When the routine is running, I found the NMAVFLG.CLA1WRITE was set, and the violated address was 0x5E02, which is the address of Sdfm1Regs.SDIFLGCLR. I guess this problem may be caused by the mapping of RAM LS8 & LS9, but I don't know if there is a way to avoid it, looking forward to your help.

Regards,

Shawn