- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Experts,

Customer use F28388D to achieve ADC 16bit mode single-ended sampling Voltage. We find that ADC sampling error very larger below:

ADC VREFHIA-D voltage is 3.0V, ADC analog Pin input Voltage/single-ended is 0~3.0V. We test different voltage on analog Pin/B2/B3. there are very larger error between actual and theoretical values.

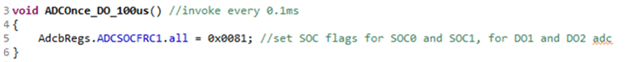

You can see the below customer's code. they use S/W trigger SOC signal on B2/B3 pin.

In addition, we eliminate the influence of memory cross talk, modify the above code, and only retain B2 per SOC for ADC sampling. we found that there is still a large deviation between the actual value and the theoretical value.

When Voltage = 2.546V,ADC Result value is 53750,but the theoretical values is 55617.

When Voltage = 2.349V,ADC Result value is 49520,but the theoretical values is 51313.

Could you help us review code and some suggestion/Dir? Thanks.

Hi Experts,

I see our example code as below:

// (single-ended mode is only a valid mode for 12-bit resolution) This is apply for F2837x, but F2838x do have 16bit mode single-ended.

F2838x Datasheet.

Hi Experts,

Do you think it is reasonable? If it is a reasonable error, how to improve the accuracy of the ADC? Thanks.

Hello Shaoxing, I will look into this and get back to you, I may need to confer with some other experts.

Can the customer please provide a screenshot of their scope measuring the voltage applied to the pin (please have them zoom in so that I can see the noise and its peaks/troughs)? Are they using any sort of buffering to reduce noise/error? Are they supplying a signal from their system or a power supply/signal generator tool? If it's the latter, the supplied signal will need to be of higher resolution than the ADC to make sure that it is a valid test of the actual voltage.

Also please note that while the ENOB for 16-bit single ended and 16-bit differential are close, these are only typical values and single-ended mode is more susceptible to noise especially because it has a higher resolution. For instance, a 0.1V noise results in about 6553 LSB of noise for 16-bit single-ended, whereas the same voltage on 12-bit single-ended is only about 410 LSB.

Hi Amir,

Very thanks for your prompt reply.

I will ask customer provide a screenshot of their scope measuring the voltage applied to the pin, meanwhile, I also ask customer test the ADC sampling with signal generator tool applied to the pin. Single channel ADC sampling will have about 2000LSB//0.033V, even if we tested EVM with same operation, also we can see about 2000LSB//0.033V. Do you think is it reasonable follow up the below ADC error.

Hi Shaoxing,

In addition to scope shots, can customer provide the input circuit? One other observation - ADCA is configured to ACQPS of 200. ADCB is configured to ACQPS of 400. When customer is converting on ADCB, is ADCA converting as well? Just wanted to confirm this so we know the ADCs are operating asynchronously, which could be a reason too for the deviation.

Regards,

Joseph

Hi Amir and Joseph,

Please see the input circuit to F28388D, The range of DOUT2 is 0V~30.98V, the range of DO2_low_level_diagnostic_ADC1 is 0~3V, corresponding to ADC result count 0~65535.

1.When we remove D23, C126, and R400, directly different voltage apply to TP143, route to F28388D analog Pin B2, tested ADC sampling error both less than 2000LSB.

2.When we keep D23, C126, and R400, tested ADC sampling error will existed lager error here.

Do you have any better recommended value for impedance ratio? Thanks.

When customer is converting on ADCB, is ADCA converting as well? Just wanted to confirm this so we know the ADCs are operating asynchronously, which could be a reason too for the deviation.

Hi Joseph,

Customer only trigger ADCB SOC signal below. ADCA is not converting when ADCB module work. If two ADC module work asynchronously, how to improve this performance? Due to different input circuit, there are different ACQPS Value here. Thanks.

Hi Shaoxing,

Regarding asynchronous operation, there will be degradation in performance as specified in datasheet. If the degradation is not acceptable then recommendation is to have all the ADCs trigger at the same time and ensure that the ACQPS is the same for the ADCs.

With regards to the input circuit, I do not see how to improve the resolution any further without using a buffer for impedance isolation and signal conditioning. For non-buffered signal feeding the ADC input, the optimum setup to match the F28388Ds analog input is few hundred ohms of source resistance and input capacitance less than 100pF. Looking at the voltage divider values to scale down the ~31V input to the analog level of the F28388D, the equivalent impedance evaluates to 56Kohms. Just doing a rough calculation of the ACQPS to get an accuracy/settling to within 100 codes requires ACQPS of 8,400 in 16 bit mode (refer to section 20.13.2 Choosing Acquisition Window in TRM). The max value for ACQPS is 511 so this means that the input signal will never settle to a low value. Customer can reduce the voltage divider resistor values but even then equivalent impedance would still put it to within a few Kohms range, which is still very high. Reducing the divider resistance further will load the ~31V source and will require high power resistors so it is also not practical.

It seems that the intent of this conversion is to monitor the 31V input line. Just wanted to understand why this cannot be accomplished in 12-bit mode. Issue with using 16-bit single-ended mode for this application is that the ADC will be more sensitive to picking up noise compared to 12-bit mode level.

Regards,

Joseph