Part Number: TMS320F28377D

That means CPU1 has its own CPUtimer0/1/2, CPU2 also has its own CPUtimer0/1/2.

Or they muxed use them?

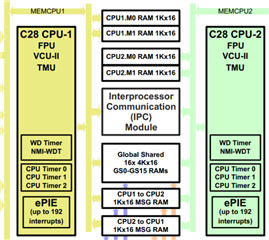

We find this diagram in datasheet:

But My customer said when he use both of CPU1 and CPU2's timer0, the CPU2's doesn't work. The configurations are the same. Only change the CPU2's timer0 to timer1, It can work.

--

Thanks & Regards