Part Number: TMS320F280049

Hi, TI experts,

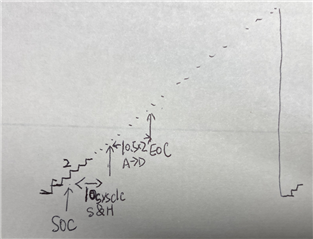

I have a project based on TIDM-DC-DC-BUCK-DC-DC Synchronous Buck Converter. The flow of the program is shown in the chart:

1. EPWM is set to up counting by EPWM_setTimeBaseCounterMode(BUCK_DRV_EPWM_BASE, EPWM_COUNTER_MODE_UP);

2. ADC conversion is triggered at the second clock of the PWM cycle, EPWM_setCounterCompareValue(BUCK_DRV_EPWM_BASE,EPWM_COUNTER_COMPARE_B,EPWM_ADC_TRIGGER_TBCTR);

3. It takes 10 sysclc(also PWM clock) for sample and hold; it takes 10.5x2 pwm clc to convert, because the pre-scale for ADC is 2;

ADC_setupSOC(VOUT_ADC_MODULE,VOUT_ADC_SOC_NO,VOUT_ADC_TRIG_SOURCE,VOUT_ADC_PIN,VOUT_ADC_ACQPS_SYS_TICKS);

4. at the EOC, InterruptServiceRouting is triggered. In ISR() function, the first thing is to check the pwm counter number isrEnter_ticks = EPWM_getTimeBaseCounterValue(BUCK_DRV_EPWM_BASE);

Based on the 4 steps above, my estimation of isrEnter_ticks should be 2+10+21=33, however, the result i got is 370(when switching frequency is set to 200kHz, which means PWM period counter is set to 500), and i got 270(when switching frequency is set to 250kHz, which means PWM period counter is set to 400).

I didn't change the values from the demo project TIDM-DC-DC-BUCK-DC-DC, you can check the parameter values assigned to the functions.

Can you help me on this?