Hi all,

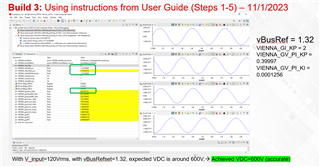

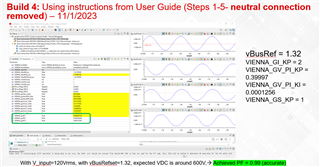

I have completed testing the TIDM-1000 from Build 1 to Build 4 and operates normally.

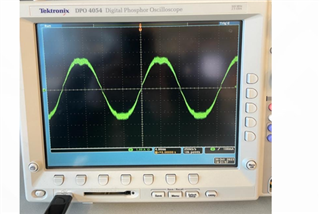

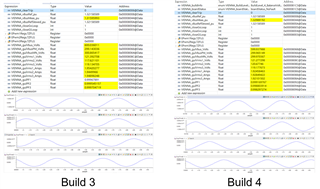

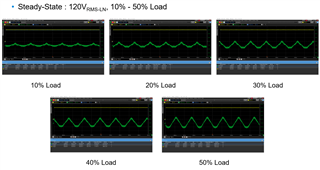

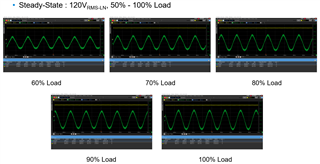

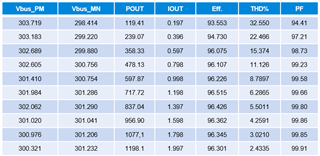

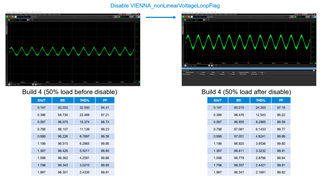

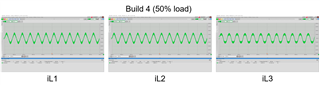

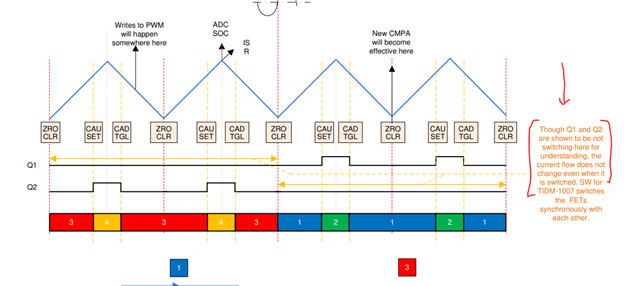

However, I encountered the same issue as this article. In Build 4 the iTHD is more larger than Build 3.(After disconnecting the bus voltage midpoint and the neutral point.)

e2e.ti.com/.../tms320f280049-tidm1000-balance-voltage-loop-question-large-thd

Unfortunately, there was no solution. Is there anyone who can provide some suggestions or solutions?

Regards,

Lyon

Attachment :

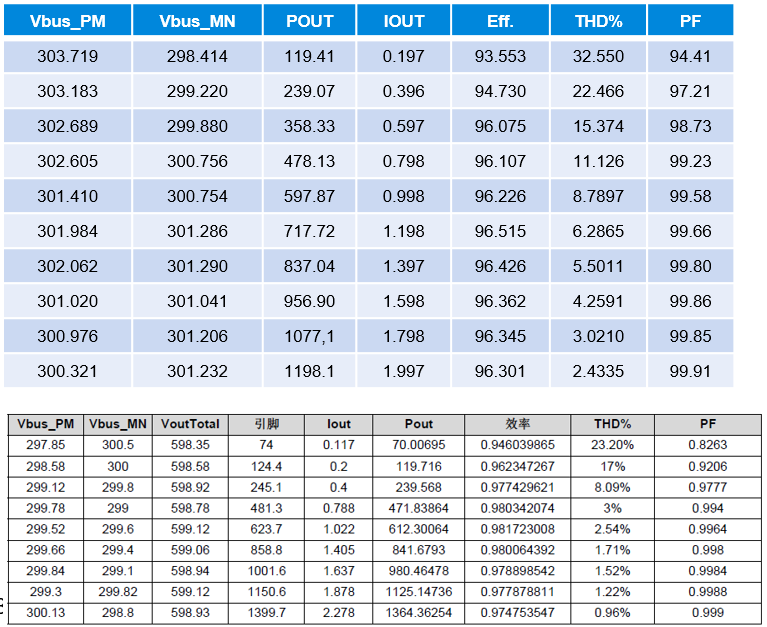

1.The table at the top is actual measurements in Build 4, the below is provided by the TIDM-1000 Design Guide.

AC input is 208Vrms L-L, 60Hz

2. The current waves of build 3 and build 4