Part Number: TMS320F28384D

Dear Sir ,

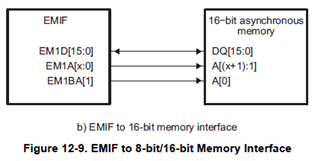

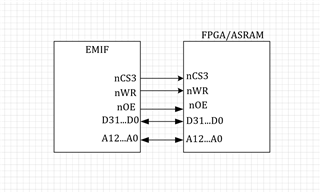

We are developing Controller based on C2000 28384D , And Accessing FPGA Registers and Memory using EMIF interface in ASRM mode 32bit Data width configuration.

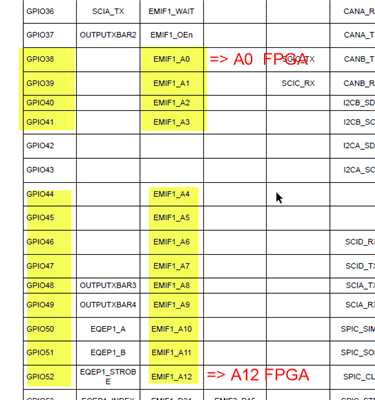

for the addresses we have connected A0...A12 , and Data D31..D0.

the Access is done via CS3 (e.g. Address range starting at 0x300000 ....).

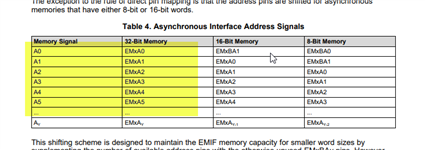

we are seeing some shift in the address , that is unclear to us . if we have access of 32bit only (using DMA/CPU ) we expected that the access to the next address will be +1

(we are probing the Address bus from A0...A12 )

e.g.

*(long *)0x300000=0; // A0...A12 all 0

*(long *)0x300001=1; //A0 =1 , A1..A12 all 0

*(long *)0x300002=2; //A0 =0 , A1 =1 , A2..A12=0

...

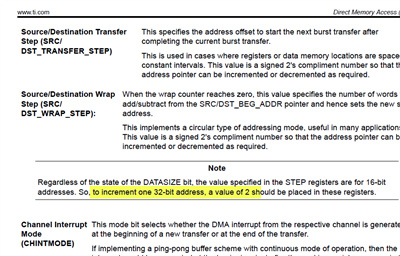

but the above is not true (this was tested with DMA in 32bit mode , and using CPU) , we are seeing some shift as shown below , it looks like that in order to access to the next address we need to add +2

*(long *)0x300000=0; // A0...A12 all 0

*(long *)0x300002=1; //A0 =1 , A1..A12 all 0

*(long *)0x300004=2; //A0 =0 , A1 =1 , A2..A12=0

this is how it is supposed to work ? i assumed that if i am accessing the FPGA as 4Kx32bit memory each address will be separated by +1