Hello,

I want to check the ROM/RAM size used.

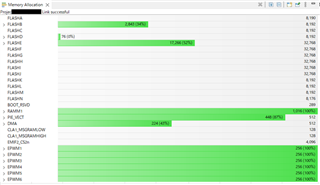

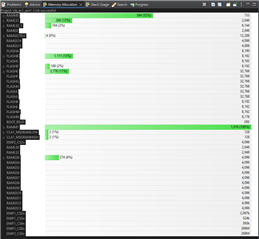

I know that there are Memory Allocation Window and mapfile in which I can see the used ROM size.

But I'm confused because the used ROM sizes in both of them are not matched.

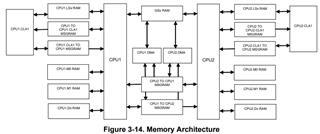

And I can't find used RAM size anywhere.

So could you teach me how to chech the actual value of used ROM/RAM size?

Thank you.

Miura.