Part Number: TMS320F280039C

Hi Team,

Customers encountered the problem of unstable AD module sampling when using F280039. The phenomenon is that the external signal sent to the AD port is stable and clean, but after the AD-converted signal inside the MCU is printed out through the DAC, it is found that there is a lot of interference on the signal, as shown in the figure below. The input signal of the ADC is a 0-3.3V sampling signal.

Yellow and green are the values in the internal ADC module result register output by the DAC, it looks like there is a problem with the AD module working.

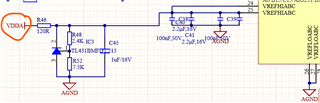

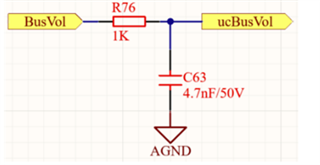

The following is the customer's configuration of the ADC module, using external power supply.

--

Thanks & Regards