Other Parts Discussed in Thread: TMDSDOCK28379D

We are currently working with the following TI components:

- TMDSDOCK28379D dev hardware.

- C2000 Ware 5.00

- CSS 12.40

The board clocks are configured as follows:

- CPU1.SYSCLK = 200MHz

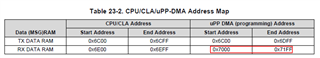

In the TMS320F2837xS Reference Manual (SPRUHX5G–August 2014–Revised September 2019) para 23.4.9 & table 23-2 describes the access to the message RAMs from the DMA & CPU/CLA views. Based on the address ranges specified, it seems that the address ranges have been swapped (typo).

Can someone confirm this?