Part Number: TMS320F28377D

Other Parts Discussed in Thread: SN54LVTH16245A

Hi Team,

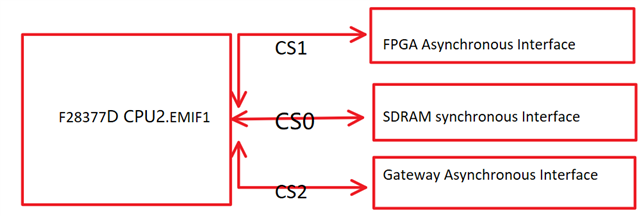

The system architecture is as follows:

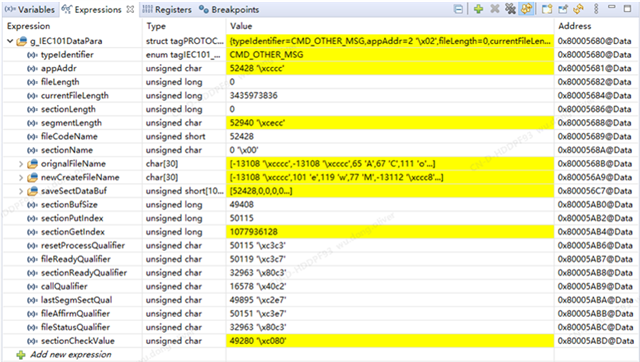

During the test, it was found that if the asynchronous device gateway is mounted, the data in the synchronous device SDRAM is unstable, as shown in the figure below. Unplug the gateway and the SDRAM data will be stable.

Use an oscilloscope to test the chip and select CS0 (SDRAM) and CS2 (gateway), as shown below:

What are the possible reasons for unstable SDRAM data?

Best Regards,

Zane