Part Number: TMS320F28P650DK

Other Parts Discussed in Thread: C2000WARE, TMDSCNCD28P65X

Hi experts,

My board can standalone boot up, and operate is normal.

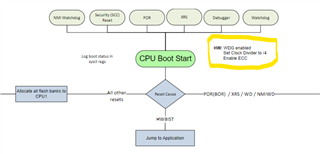

But, when the reset occur on CPU1 - WDT reset or the reset occur on CPU2 to trig CPU1 - NMIWDT ISR timeout reset, the CPU1 cannot reset success.

I refernced TI example code - CPU2 WDT reset & CPU1 NMIWDT ISR trig to reset CPU2 can success. So, I think CPU2 reset is OK.

Another TI example code - CPU1 WDT ISR isn't match my application, this example code set WDT mode is ISR mode, so I didn't test.

By the way, when I reset CPU1, and then using JTAG connect to download code & restart, I can see the WDT REG - WDRSn ( watchdog reset flag ) is ON. I think CPU1 WDT function is normal, but restart is fail.

Hence, I want to know how to solve the question of CPU1 WDT reset or NMIWDT reset?

Thanks.

B.R.

Bolt