Other Parts Discussed in Thread: C2000WARE

We are working on developing Bootloader for upgrading the firmware over Ethercat protocol using TMS320f28388 development board. We have referred the document “spruiu8a_lfu” provided by TI for live firmware update.

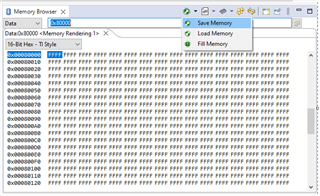

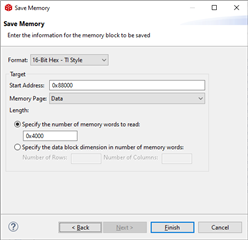

Here Bootloader/ kernel is placed in the first four sectors of flash memory and start executing at the default flash boot address 0x80000.

The Application code is placed in the rest 10 sectors of the flash memory and start executing on the Alternate flash address 0x88000.

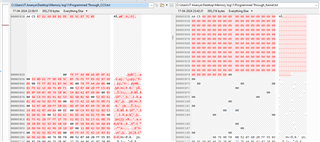

Tha Bootloader/ kernel is programmed using CCS, after every power reset, the bootloader/kernel code starts executing at the default flash address 0x80000 and looks for the key 0x5A5A5A5A stored in the end of the third sector. If the kernel finds the key, then it assumes that the Application is programmed already into the flash, and it calls the entry address of the application code as asm(" LB 0x00088000").

IF the kernel does not find the key, then it assumes that no Application code is present in the flash memory and it waits for user input to programmer the application code into the flash memory, after the programming it writes KEY value 0x5A5A5A5A into the end of kernel flash sector.

Here the Problem we are getting is , Once the kernel finds the key and calls the application using assembly instruction "asm(" LB 0x00088000")" , the code is not getting executed and staying at the reset vector.

Here I have verified about the memory regions allocated and the generated after compiling I didn’t find any issue and there is no overlapping between kernel and the Application.

So, requesting to please suggest any way to resolve this, your help will be appreciated lot.

The memory partition is as below.

Bootloader code

----------------------

#pragma CODE_SECTION(bankSelect, "codestart");

void bankSelect(void)

{

if((HWREG((uint32_t)B0_KEY_ADD) != (uint32_t)KEY))

{

CPU1_Kernel();

}

else

{

//

// Branch to 0x00088000; the codestart of bank 0 is

// located at 0x00088000, which is a flash alt. entry point

//

asm(" LB 0x00088000");

}

}

bootloader memory configuration .cmd file

--------------------------------------------

// Keep the _bankSelect symbol

//

-u bankSelect

MEMORY

{

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000100

BOOT_RSVD : origin = 0x000002, length = 0x0001AF /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x0001B1, length = 0x00024F

RAMM1 : origin = 0x000400, length = 0x0003F8 /* on-chip RAM block M1 */

RAMM1_RSVD : origin = 0x0007F8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMD0 : origin = 0x00C000, length = 0x000800

RAMD1 : origin = 0x00C800, length = 0x000800

//RAMD01 : origin = 0x00C000, length = 0x001000

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMGS0 : origin = 0x00D000, length = 0x001000

RAMGS1 : origin = 0x00E000, length = 0x001000

RAMGS2 : origin = 0x00F000, length = 0x001000

RAMGS3 : origin = 0x010000, length = 0x001000

RAMGS4 : origin = 0x011000, length = 0x001000

RAMGS5 : origin = 0x012000, length = 0x001000

RAMGS6 : origin = 0x013000, length = 0x001000

RAMGS7 : origin = 0x014000, length = 0x001000

RAMGS8 : origin = 0x015000, length = 0x001000

RAMGS9 : origin = 0x016000, length = 0x001000

RAMGS10 : origin = 0x017000, length = 0x001000

RAMGS11 : origin = 0x018000, length = 0x001000

RAMGS12 : origin = 0x019000, length = 0x001000

RAMGS13 : origin = 0x01A000, length = 0x001000

RAMGS14 : origin = 0x01B000, length = 0x001000

RAMGS15 : origin = 0x01C000, length = 0x000FF8

// RAMGS15_RSVD : origin = 0x01CFF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* Flash sectors */

IPC_FLASH_MY : origin = 0x080100, length = 0x000100 /* on-chip Flash */

FLASH0 : origin = 0x080200, length = 0x001E00 /* on-chip Flash */

FLASH1 : origin = 0x082000, length = 0x002000 /* on-chip Flash */

FLASH2 : origin = 0x084000, length = 0x002000 /* on-chip Flash */

FLASH3 : origin = 0x086000, length = 0x002000 /* on-chip Flash */

FLASH4 : origin = 0x088000, length = 0x008000 /* on-chip Flash */

FLASH5 : origin = 0x090000, length = 0x008000 /* on-chip Flash */

FLASH6 : origin = 0x098000, length = 0x008000 /* on-chip Flash */

FLASH7 : origin = 0x0A0000, length = 0x008000 /* on-chip Flash */

FLASH8 : origin = 0x0A8000, length = 0x008000 /* on-chip Flash */

FLASH9 : origin = 0x0B0000, length = 0x008000 /* on-chip Flash */

FLASH10 : origin = 0x0B8000, length = 0x002000 /* on-chip Flash */

FLASH11 : origin = 0x0BA000, length = 0x002000 /* on-chip Flash */

FLASH12 : origin = 0x0BC000, length = 0x002000 /* on-chip Flash */

FLASH13 : origin = 0x0BE000, length = 0x001FF0 /* on-chip Flash */

// FLASH13_RSVD : origin = 0x0BFFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000800

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000800

CPUTOCMRAM : origin = 0x039000, length = 0x000800

CMTOCPURAM : origin = 0x038000, length = 0x000800

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

codestart : > BEGIN, ALIGN(8)

.text : >> FLASH0 | FLASH1, ALIGN(8)

.cinit : > FLASH1, ALIGN(8)

.switch : > FLASH5, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMD0

#if defined(__TI_EABI__)

.init_array : > FLASH1, ALIGN(8)

.bss : > RAMLS5

.bss:output : > RAMLS5

.bss:cio : > RAMLS5

.data : > RAMLS5

.sysmem : > RAMLS5

/* Initalized sections go in Flash */

.const : > FLASH1, ALIGN(8)

#else

.pinit : > FLASH1, ALIGN(8)

.ebss : > RAMLS5

.esysmem : > RAMLS5

.cio : > RAMLS5

/* Initalized sections go in Flash */

.econst : >> FLASH1 , ALIGN(8)

#endif

ramgs0 : > RAMGS0, type=NOINIT

ramgs1 : > RAMGS1, type=NOINIT

MSGRAM_CPU1_TO_CPU2 : > CPU1TOCPU2RAM, type=NOINIT

MSGRAM_CPU2_TO_CPU1 : > CPU2TOCPU1RAM, type=NOINIT

MSGRAM_CPU_TO_CM : > CPUTOCMRAM, type=NOINIT

MSGRAM_CM_TO_CPU : > CMTOCPURAM, type=NOINIT

/* The following section definition are for SDFM examples */

Filter_RegsFile : > RAMGS0

Filter1_RegsFile : > RAMGS1, fill=0x1111

Filter2_RegsFile : > RAMGS2, fill=0x2222

Filter3_RegsFile : > RAMGS3, fill=0x3333

Filter4_RegsFile : > RAMGS4, fill=0x4444

Difference_RegsFile : >RAMGS5, fill=0x3333

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH0,

RUN = RAMLS0|RAMLS1|RAMLS2|RAMLS3,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASH0,

RUN = RAMLS0|RAMLS1|RAMLS2|RAMLS3,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

IPC_BANK0 : > IPC_FLASH_MY, PAGE = 0, ALIGN(8)

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

Application memory configuration .cmd file

--------------------------------------------

MEMORY

{

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x088000, length = 0x000002

BOOT_RSVD : origin = 0x000002, length = 0x0001AF /* Part of M0, BOOT rom will use this for stack */

RAMM01 : origin = 0x0001B1, length = 0x000647

// RAMM0 : origin = 0x0001B1, length = 0x00024F

// RAMM1 : origin = 0x000400, length = 0x0003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x0007F8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMD0 : origin = 0x00C000, length = 0x000800

RAMD1 : origin = 0x00C800, length = 0x000800

//RAMLS0 : origin = 0x008000, length = 0x000800

//RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS0LS1 : origin = 0x008000, length = 0x001000

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800

RAMGS0 : origin = 0x00D000, length = 0x001000

RAMGS1 : origin = 0x00E000, length = 0x001000

RAMGS2 : origin = 0x00F000, length = 0x001000

RAMGS3 : origin = 0x010000, length = 0x001000

RAMGS4 : origin = 0x011000, length = 0x001000

RAMGS5 : origin = 0x012000, length = 0x001000

RAMGS6 : origin = 0x013000, length = 0x001000

RAMGS7 : origin = 0x014000, length = 0x001000

RAMGS8 : origin = 0x015000, length = 0x001000

RAMGS9 : origin = 0x016000, length = 0x001000

RAMGS10 : origin = 0x017000, length = 0x001000

RAMGS11 : origin = 0x018000, length = 0x001000

RAMGS12 : origin = 0x019000, length = 0x001000

RAMGS13 : origin = 0x01A000, length = 0x001000

RAMGS14 : origin = 0x01B000, length = 0x001000

RAMGS15 : origin = 0x01C000, length = 0x000FF8

// RAMGS15_RSVD : origin = 0x01CFF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* Flash sectors */

FLASH0 : origin = 0x080000, length = 0x002000 /* on-chip Flash */

FLASH1 : origin = 0x082000, length = 0x002000 /* on-chip Flash */

FLASH2 : origin = 0x084000, length = 0x002000 /* on-chip Flash */

FLASH3 : origin = 0x086000, length = 0x002000 /* on-chip Flash */

BTDC_APP_FLASH : origin = 0x088050, length = 0x001000

FLASH4 : origin = 0x089050, length = 0x006FB0 /* on-chip Flash */

FLASH5 : origin = 0x090000, length = 0x008000 /* on-chip Flash */

FLASH6 : origin = 0x098000, length = 0x008000 /* on-chip Flash */

FLASH7 : origin = 0x0A0000, length = 0x008000 /* on-chip Flash */

FLASH8 : origin = 0x0A8000, length = 0x008000 /* on-chip Flash */

FLASH9 : origin = 0x0B0000, length = 0x008000 /* on-chip Flash */

FLASH10 : origin = 0x0B8000, length = 0x002000 /* on-chip Flash */

FLASH11 : origin = 0x0BA000, length = 0x002000 /* on-chip Flash */

FLASH12 : origin = 0x0BC000, length = 0x002000 /* on-chip Flash */

FLASH13 : origin = 0x0BE000, length = 0x001FF0 /* on-chip Flash */

// FLASH13_RSVD : origin = 0x0BFFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000800

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000800

CPUTOCMRAM : origin = 0x039000, length = 0x000800

CMTOCPURAM : origin = 0x038000, length = 0x000800

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

codestart : > BEGIN, ALIGN(8)

.text : >> FLASH4 | FLASH5 | FLASH6 | FLASH7, ALIGN(8)

.cinit : > FLASH5, ALIGN(8)

.switch : > FLASH5, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

//.stack : > RAMLS0LS1

.stack : > RAMD0

#if defined(__TI_EABI__)

.init_array : > FLASH9, ALIGN(8)

.bss : > RAMD1

.bss:output : > RAMD1

.bss:cio : > RAMD1

.data : > RAMD1

.sysmem : > RAMD1

/* Initalized sections go in Flash */

.const : > FLASH6, ALIGN(8)

#else

.pinit : > FLASH6, ALIGN(8)

.ebss : > RAMD1

.esysmem : > RAMD1

.cio : > RAMD1

/* Initalized sections go in Flash */

.econst : >> FLASH6 | FLASH7, ALIGN(8)

#endif

ramgs0 : > RAMGS0, type=NOINIT

ramgs1 : > RAMGS1, type=NOINIT

MSGRAM_CPU1_TO_CPU2 : > CPU1TOCPU2RAM, type=NOINIT

MSGRAM_CPU2_TO_CPU1 : > CPU2TOCPU1RAM, type=NOINIT

MSGRAM_CPU_TO_CM : > CPUTOCMRAM, type=NOINIT

MSGRAM_CM_TO_CPU : > CMTOCPURAM, type=NOINIT

/* The following section definition are for SDFM examples */

Filter_RegsFile : > RAMGS0

Filter1_RegsFile : > RAMGS1, fill=0x1111

Filter2_RegsFile : > RAMGS2, fill=0x2222

Filter3_RegsFile : > RAMGS3, fill=0x3333

Filter4_RegsFile : > RAMGS4, fill=0x4444

Difference_RegsFile : >RAMGS5, fill=0x3333

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH5,

RUN = RAMLS6|RAMLS7,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASH5,

RUN = RAMLS6|RAMLS7,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

BTDC_APP : > BTDC_APP_FLASH, PAGE = 0, ALIGN(8)

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/