Hi All,

I have a question regarding the CPU boot sequence.

I am trying to follow the power sequence in the datasheet,

but CPU does not boot.

The following is a description of the conditions we have followed.

Please let us know the cause of CPU not booting.

<Conditions under which the CPU does not start up>

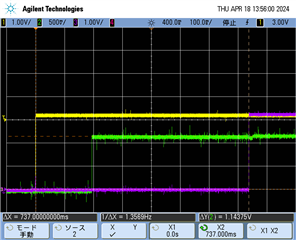

・VDD (1.2V) is started up about 200ms after VDDIO (3.3V) is started up.

(External reset release is released approximately 70ms after VDDIO start-up.)

・VDD(1.2V) was started up about 509ms after VDDIO(3.3V) was started up.

(External reset release is released approximately 70ms after VDDIO start-up.)

・VDD(1.2V) was started up about 642ms after VDDIO(3.3V) was started up.

(External reset release is released approximately 70ms after VDDIO start-up.)

・VDD(1.2V) was started up about 832ms after VDDIO(3.3V) was started up.

(External reset release is released approximately 70ms after VDDIO start-up.)

<CPU startup conditions>

・VDD(1.2V) was started up about 910ms after VDDIO(3.3V) was started up.

(External reset release is released approximately 70 ms after VDDIO startup.)

・VDD(1.2V) was started up about 1.2s after VDDIO(3.3V) was started up.

(External reset release is released approximately 70ms after VDDIO start-up.)

・When started up at a slower time than the above, it will start up at any time.

(External reset release is released approximately 70ms after VDDIO startup.)

・After starting up VDDIO (3.3V), VDD (1.2V) is started up about 200ms later,

External reset is released after approx. 1.5ms.

・The device will also start up at a slower external reset release time than the above.