Part Number: TMS320F280033

Other Parts Discussed in Thread: C2000WARE,

Hi,

My flashed code works fine on the first build but does not load after CPU reset or power cycle.

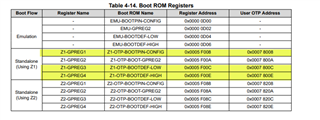

Upon CPU reset, the code is initially stuck at 0x3fdba4 with the following warning statement:

Break at address "0x3fdba4" with no debug information available, or outside of program code.

If I hit Resume, it gets stuck at 0x3fb8b9 with the statement:

Break at address "0x3fb8b9" with no debug information available, or outside of program code.

Further information:

CCS version: 12.7

Compiler version: TI v22.6.1.LTS

Output Format: eabi (ELF)

Linker command file: F280033_flash_lnk.cmd

C2000ware version: 5.02

I have added --

Predefined symbol: _FLASH

Program entry point for the output module: code_start

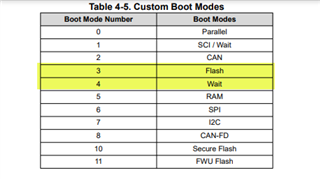

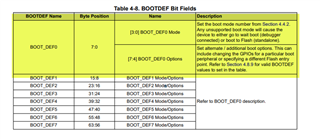

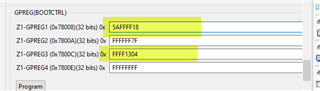

I am using TMS320F280033 on my custom hardware along with XDS100v2 debug probe. Both the boot mode pins are pulled up using 4.7k resistors.

NOTE: There was a build error with F280033_flash_lnk.cmd linker command file-

"../F280033_flash_lnk.cmd", line 45: error #10468-D: The memrange group 'MEMORY_GROUP_1' contains a gap. 'BEGIN' ends at address 0x80002 and 'FLASH_BANK0_SEC8' starts at address 0x88000. Group cannot contain gaps."

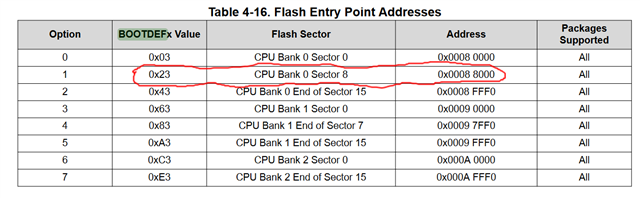

so I modified line #48 of the linker command file to -

BEGIN : origin = 0x00088000, length = 0x00000002

and line #51 to -

FLASH_BANK0_SEC8 : origin = 0x088002, length = 0x000FFE

after which I could successfully build the program and test the code. However, the problem of flashed code not loading after CPU reset or power cycle still exists.

Any help on this issue would be greatly appreciated.