hello:

i have a question that disturb me long time.

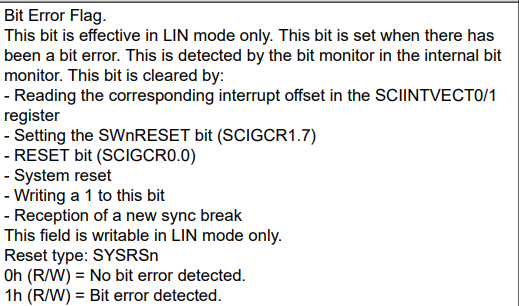

master request 3C,when 3D response ,disturbe the frame in byte1 stop bit ,it trigger a bit error, it should show in response error bit

but in fact,after service the BE error interrupt the busy bit in SCIFLR is set always, it lead the frist frame abnormal and second frame is ok

how to clear the busy bit in SCIFLR ?

how to clear the transmit buffer or receive buffer?