Hello,

I am so far not finding it in the datasheet: is there a limitation on LSPCLK setting that I need to be aware of, particularly when using SPI and SCIA?

If I set LSPCLK = SYSCLK / 2, can I use LSPCLK = 100MHz, are there any issues?

Thanks!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

I am so far not finding it in the datasheet: is there a limitation on LSPCLK setting that I need to be aware of, particularly when using SPI and SCIA?

If I set LSPCLK = SYSCLK / 2, can I use LSPCLK = 100MHz, are there any issues?

Thanks!

Hi Mark,

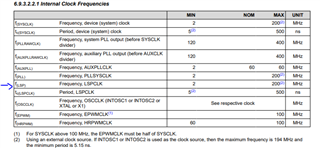

This information is provided in datasheet. Attached snapshot below

Let me know if you have any further questions

Thanks,

Prarthan

Thank you Prathan,

Part of my question...is there any issue for SPI or SCI to use faster LSPCLK?

The examples seem to use lower / default values, so I want to make sure it isn't a limitation of the SPI or SCI.

Thanks,

Mark

Hi Mark,

Yes there are limitations on max frequency from SPI or SCI perspective.

You can check the electrical specification section 6.12.5.1 SPI Electrical Data and Timing for different SPI modes and see if you have more questions so that we can seek help from SPI/SCI expert