Part Number: TMS320F28384D

Hi All,

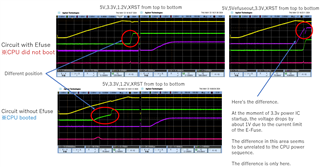

What is the cause that CPU does not start up under the following conditions?

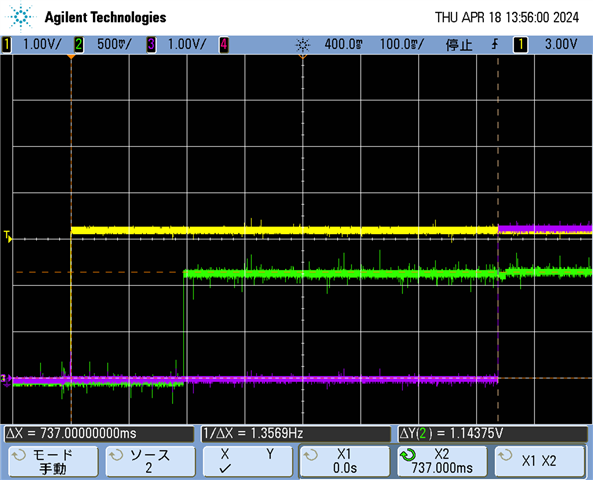

・After 3.3V starts up, 1.2V starts up about 200ms later.

When external reset is input about 530ms after that, the CPU does not start up.

・After 3.3V starts up, 1.2V starts up about 200ms later.

When external reset is input about 700ms after that, the CPU start up.

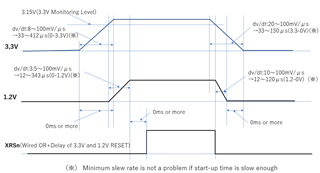

・The slew rate is 3.3mV/us for 3.3V and 6mV/us for 1.2V.

The 3.3V does not meet the value in the datasheet, but looking at the contents of the datasheet, it seems to be OK.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・

If the minimum slew rate cannot be met, a supervisor must be used on VDDIO and VDD to keep XRSn low

until VDD crosses the minimum operating voltage to ensure correct device functionality.

・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・

The waveform is shown in the following image.

I will send the schematic to a private message.

Is there a reason why the CPU does not start up after 530ms?

Best Regards,

Ito