Other Parts Discussed in Thread: DRV8300, BOOSTXL-DRV8323RS, LAUNCHXL-F280025C, LAUNCHXL-F2800157

Hi,

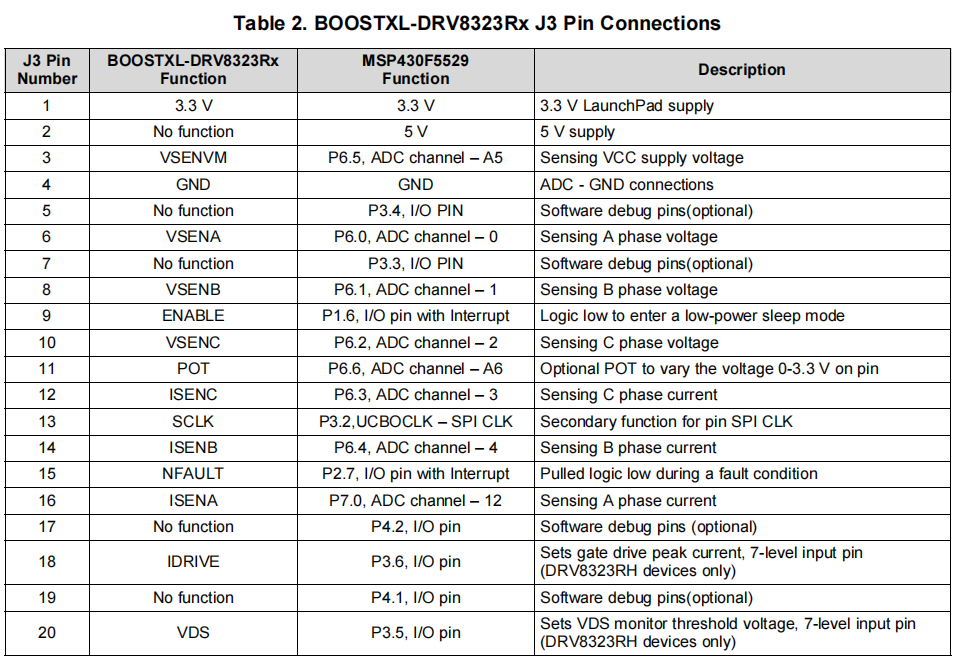

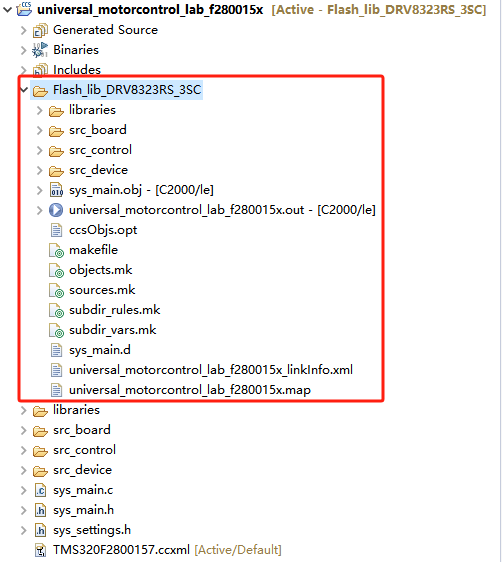

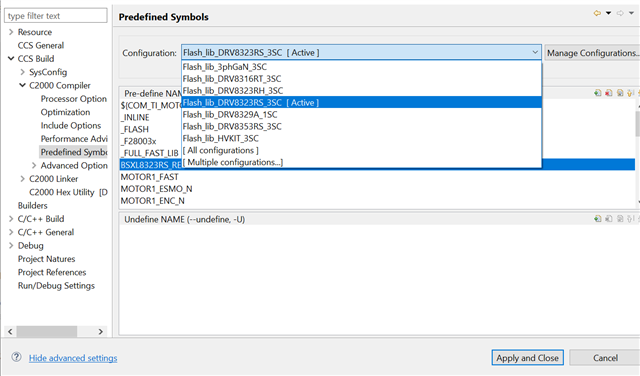

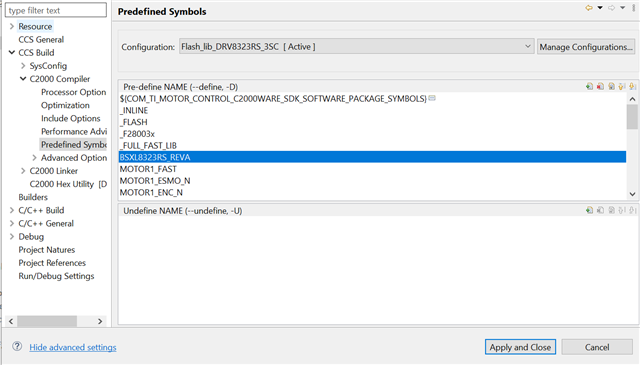

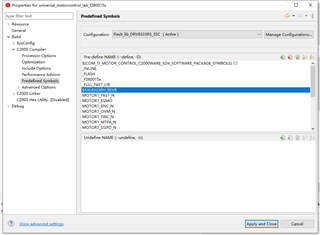

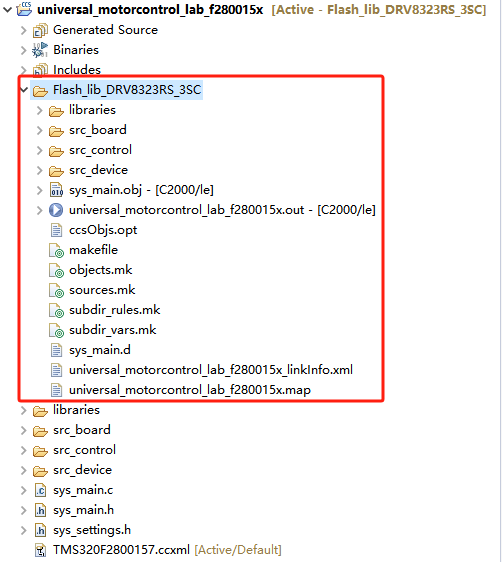

I need to use F280015x+DRV8300 for the final product. Currently, the official routine of F280015x only includes the routine of DRV8323RS. I think I should configure the case of F280015x+DRV8323RH first. Found that DRV8323RS and DRV8323RH code has a big difference, and modify the configuration is a key modification, I do not know its specific operation, can you teach me how to modify the F280015x+DRV8323RS routine, so that it can be used in the configuration of F280015x+DRV8323RH?

Thank you for any help!

Regards,

Johnny